HMC7043相关信息来自ADI官网,详细参数以官网发布为准,HMC7043供给信息可在查IC网查找相关供给商。

产品概况

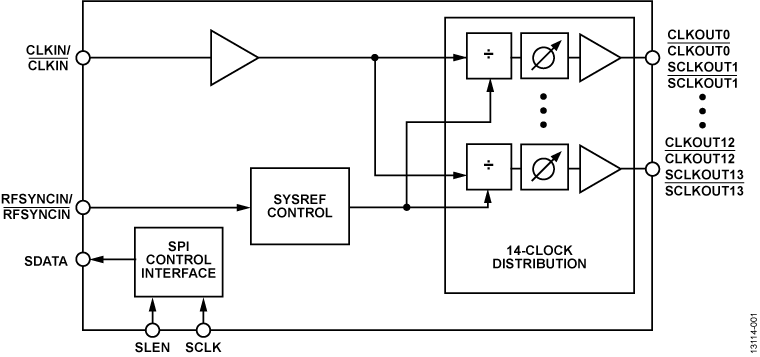

HMC7043旨在满意多载波GSM和LTE基站规划的要求,并经过多种时钟办理和分配特性来简化基带和无线电卡时钟树的规划

HMC7043供给14路低噪声且可装备的输出,能够灵敏地与基站收发台(BTS)体系中的许多不同器材接口,如数据转换器、本振、发射/接纳模块、现场可编程门阵列(FPGA)和数字前端ASIC等。 HMC7043可生成契合JESD204B接口要求的多达7个DCLK和SYSREF时钟对。

体系规划人员能够生成更少的DCLK和SYSREF对,并针对独立的相位和频率装备其他的输出信号途径。 DCLK和SYSREF时钟输出均可装备为支撑CML、LVDS、LVPECL和LVCMOS等不同的信号规范,不同的偏置条件则可调整改变的板插入损耗。

HMC7043共同的特性之一是对14个通道别离进行独立灵敏的相位办理。 一切14个通道均支撑频率和相位调整。 这些输出还可针对50 Ω或100 Ω内部和外部端接选项进行编程。

HMC7043器材具有RF SYNC功用,支撑确认性同步多个HMC7043器材,即保证一切时钟输出从同一时钟沿开端。 可经过改写嵌套式HMC7043或SYSREF操控单元/分频器,然后重新启动具有新相位的输出分频器来完成。

HMC7043选用48引脚、7 mm × 7 mm LFCSP封装,且暴露焊盘接地。

使用

- JESD204B时钟发生

- 蜂窝基础设施(多载波GSM、LTE、W-CDMA)

- 数据转换器时钟

- 相控阵参阅分配

- 微波基带卡

优势和特色

- 支撑JEDEC JESD204B

- 低加性颤动: <15 fs rms(2457.6 MHz,12 kHz至20 MHz)

- 极低噪底: -155.2 dBc/Hz (983.04 MHz)

- 最多供给14路LVDS、LVPECL或CML型器材时钟(DCLK)

- CLKOUTx/CLKOUTx and SCLKOUTx/SCLKOUTx 最高频率达 3200 MHz

- JESD204B兼容体系参阅(SYSREF)脉冲

- 25 ps模仿推迟和½时钟输入周期数字推迟,14个时钟输出通道各自都能对推迟进行编程

- 可调噪底与功耗的联系可经过SPI编程

- SYSREF有用中止可简化JESD204B同步

- 支撑确认性同步多个HMC7043器材

- RFSYNC引脚或SPI操控的SYNC触发用于输出同步JESD204B

- GPIO报警/情况指示用于确认体系情况

- 时钟输入支撑高达6 GHz的频率

- 片内稳压器供给超卓的PSRR

- 48引脚、7 mm × 7 mm LFCSP封装

HMC7043电路图

HMC7043中文PDF下载地址

HMC7043下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/HMC7043.pdf