导言

低密度奇偶校验(Low Density Parity Check Code,LDPC)码是一类具有稀少校验矩阵的线性分组码,不只有迫临Shannon限的杰出功能,并且译码复杂度较低, 结构灵敏,是近年信道编码范畴的研讨热门,现在已广泛应用于深空通讯、光纤通讯、卫星数字视频和音频播送等范畴。LDPC码已成为第四代通讯体系(4G)强有力的竞争者,而依据LDPC码的编码计划现已被下一代卫星数字视频播送规范DVB-S2选用。

编码器完结目标剖析

作为前向纠错体系的重要部分,规划高速率低复杂度LDPC码编译码器成为进步体系功能的要害。对LDPC码来说,其编码复杂度相对较大,编码器的规划与完结是首要任务,也是译码器规划与完结的条件,有着十分重要的效果。

编码速率与复杂度是点评LDPC编码器好坏的重要目标。考虑高清晰度电视(HDTV)规范在分辨率为1920×1080,帧率为60帧/s,每个像素以24比特量化时,总数据率在2Gb/s的数量级。选用MPEG-2紧缩,要求数据率大约在20~40Mb/s。

编码器规划思路

设LDPC码查验矩阵为H、生成矩阵为G 。传统的编码方法是运用生成矩阵G直接进行编码。因为G并不具有稀少性,直接编码的复杂度与码长N的平方成正比。本文的编码器选用RU编码算法。该算法经过对交流校验矩阵队伍的方位,坚持矩阵的稀少性,运用交流队伍后的校验矩阵进行编码,有用下降了编码的复杂度。经过队伍交流的校验矩阵具有近似下三角方式,如图1所示。

图1 交流校验矩阵

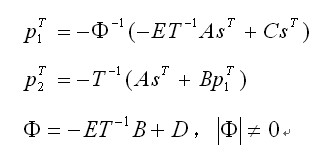

设信息序列为s,码字为C运用图1的矩阵可对信息序列s进行编码。码字分为三部分:C=(s,p1,p2),其间s是信息比特序列,长度为k;p1和p2是校验比特序列,长度别离为g和N-k-g。校验比特序列p1、p2核算公式如下:

编码流程如图2所示。

图2 编码流程图

规划LDPC编码器的时分留意:在RU算法中,对校验矩阵进行队伍交流,转化为近似下三角方式称为编码预处理进程。给定一个校验矩阵,编码预处理进程和矩阵的核算只需要做一次,所以可先用软件完结。实践的编码核算经过硬件完结。这样做有利于进步编码硬件完结的功率。

LDPC码编码器完结

LDPC码编码器硬件结构

依据RU算法的LDPC编码完结进程主要是核算p1、p2的进程。规划编码器时,为了进步编码速度,将能够一起核算的进程作并行处理,得到编码器的硬件结构如图3所示。

图3 LDPC码编码器结构

图3中A、B、C、E别离代表图1中相应的矩阵,F代表Φ矩阵。从图3可知,LDPC编码器主要由缓冲器(buffer)、矩阵向量乘法器(MVM)、矩阵加法器(VA)、前向迭代运算器(FS)、向量组成器(CWG)等运算单元以及存储各个矩阵相关信息的存储器组成。因为前向迭代运算根本上是矩阵与向量的乘法核算,所以矩阵向量乘法是LDPC编码进程最中心的单元。

剖析图3可知,编码进程中,Cs与As的核算是一起进行的,其他的操作都是串行进行的。因为队伍交流坚持了矩阵的稀少性,所以与A、B、C、E矩阵的相关运算是稀少矩阵的运算,存储矩阵所需的空间少一起完结的复杂度低和运算速度快。Φ是g×g的矩阵,因为在编码预处理进程中确保了g尽量小,所以与Φ矩阵相关的运算也是比较快的。

LDPC码编码器复杂度

表1和表2描绘了编码器核算校验序列p1、p2的流程及相应的复杂度。

表1 p1的核算

表2 p2的核算

从表1和表2可知RU算法的复杂度与N+g2成正比,g越小,编码复杂度越低。所以对校验矩阵进行队伍交流时,使g尽量小是进一步下降编码复杂度的要害。

表1中序号2与表2中序号4的操作触及到下三角矩阵T。因为T-1也是下三角矩阵,为了下降复杂度,可选用前向迭代进行核算。例如:假定Qx=y,Q为下三角矩阵,求x。核算进程如下:

编码器中心模块——矩阵向量乘法器(MVM)的完结

矩阵与矩阵的乘法运算以及前向迭代运算实质上都是矩阵与向量的乘法。下面举例阐明矩阵向量乘法器硬件完结的进程:

假定,关于LDPC编码器,怎么有用率地存储各个矩阵的信息是下降复杂度的要害。下面给出一种矩阵存储的计划:矩阵存储器中记载“1”内行中的方位以及对应行行重,如表3所示。例如矩阵X第3行的“1”元素,内行中的方位为“0”,该行的行重为1。因为LDPC编码进程中运用的矩阵大多是稀少矩阵,所以选用该矩阵存储计划能比较有用地运用存储的空间并有利于矩阵与向量乘法的快速完结。

矩阵X每行中“1”的方位可看作挑选向量s相应元素的地址索引,将挑选的一切元素相加作和,即完结X中某行与向量的运算。因为触及的运算都是二进制加法,相加作和操作能够作如下简化:依据矩阵每行“1”的方位挑选向量s的元素。核算被挑选的元素中“1”的个数,若成果为奇数则阐明相加的成果为“1”,不然阐明相加的成果为“0”。判别成果为奇数或许偶数可由其二进制方式的末位是“1”或许“0”得到。经过设置两个计数器别离核算各行行重和挑选的向量s相应方位的元素中“1”的个数,即可完结乘法单元的运算。

矩阵向量乘法器的硬件结构如图4所示。

图4 矩阵向量乘法器的硬件结构

从图4可知矩阵向量乘法器包含以下六个部分:调度单元(Scheduler),发生各模块单元的使能信号;缓存单元(Info_buffer),对输入信息序列进行缓存处理;存储器操控单元(Rom_ctrl),发生存储器的地址信号;“1”方位存储器(Rom_num),存储矩阵各行“1”的方位;行重存储器,存储矩阵相应各行行重;乘法单元(Multipler),进行向量乘法运算,最终输出码字。

矩阵向量乘法器仿真成果验证

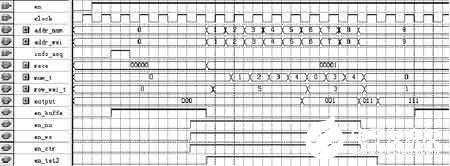

在Quartus II环境下,完结output=Xs,得到如图5所示时序图。

图5 output=“Xs仿真时序图”

图5中“en”是使能信号,“clock”是时钟信号,addr_num、addr_wei别离为两个存储器的地址信号,info_seq是输入信息信号,rece是信息信号经过缓存后的输出信号,num_t是“1”在各行的方位信息,row_wei_t是相应各行的行重,output是矩阵与向量相乘的成果。由图5可知,output=[1 1 1],信号输出有一个时钟周期的延时,仿真成果正确。

编码器计划验证与优缺点剖析

本文运用FPGA完结了依据RU算法的编码器规划完结。在Quartus II软件环境下对LDPC编码器进行仿真,运用StraTIx系列EP1s25F672I7芯片,对码长为504的码字进行编码。编码器占用约9%的逻辑单元,约5%的存储单元,归纳后时钟频率到达120MHz,数据吞吐率到达33Mb/s,根本契合编码器规划的要求。该编码器结构是一种通用的规划计划,能够应用于各种不同的LDPC编码中,但因为其选用通用的编码算法,完结的复杂度高于某些特别结构的LDPC码编码器,比方准循环LDPC码。别的经过优化时序和编码结构,能够进一步进步本文的编码器的编码速度。

责任编辑:gt