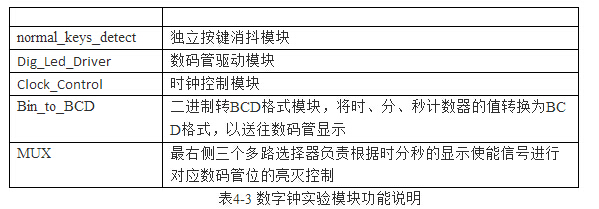

图中存在较多的模块,因而在此将每个模块的功用做简略介绍:

别的,Clock_Control模块为归纳模块,内部包含了时、分、秒、时钟计数器模块和时刻设定模块,该模块的内部结构这儿小梅哥不做过多介绍,具体请参看代码。

五、 代码安排方法

本试验首要学习由顶向下的规划流程,代码均为常见风格,这儿不多做介绍。期望读者可以经过代码架构,学习体会这种自顶向下的规划结构的优势。

六、 要害代码解读

本规划中,顶层模块首要完成了各个模块的例化和数码管显现使能的多路操控,信任看了图4-1后,便能了解顶层代码的意义。由于本体系涉及到的模块较多,选用文档的方法很难简练的解说清楚,因而,归纳试验,小梅哥今后将不再进行要害代码的解读。反之,小梅哥会尽快进行视频的录制,对归纳试验选用视频的方法解说,以使读者快速了解架构。

七、 测验渠道规划

本体系为低速体系,选用Modelsim仿真耗时长,并且波形不便于调查。因而仿真省略。我们可以对每个子模块进行仿真,以验证其正确性。

八、 仿真剖析

九、 下板验证

此次,小梅哥选用很早以前购买的21EDA的板子进行了下板测验,实测功用齐备。以下为测验相片(渣渣像素,请各位体谅)。

十、 总结

本试验完成了数码钟的功用,并可以经过4个按键进行时刻的设置,由于时刻的联系,小梅哥没有在文档中进行具体的介绍,请我们体谅。