1.FPGA概述

FPGA是英文FieldProgrammableGateArray的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器材的基础上进一步开展的产品。它是作为专用集成电路(ASIC)领域中的一种半定制电路而呈现的,既处理了定制电路的缺乏,又克服了原有可编程器材门电路数有限的缺陷

2.FPGA芯片结构

FPGA芯片首要由三部分组成,分别是IOE(inputoutputelement,输入输出单元)、LAB(logicarrayblock,逻辑阵列块,关于Xilinx称之为可装备逻辑块CLB)和Interconnect(内部连接线)。

2.1 IOE

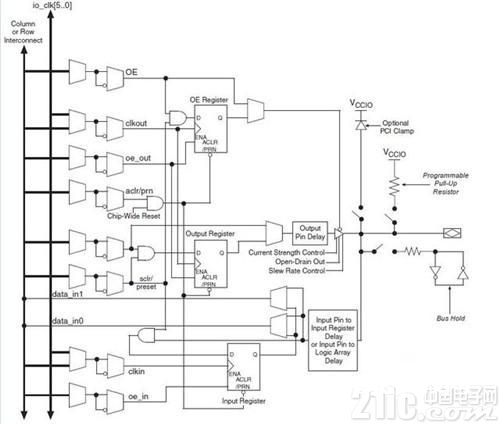

IOE是芯片与外部电路的物理接口,首要完结不同电气特性下输入/输出信号的驱动与匹配要求,比如从根本的LVTTL/LVCMOS接口到PCI/LVDS/RSDS乃至各式各样的差分接口,从5V兼容到3.3V/2.5V/1.8V/1.5V的电平接口,下面是ALTERA公司的CycloneIVEP4CE115F29设备的IOE结构

EP4CE115F29设备的IOE结构图

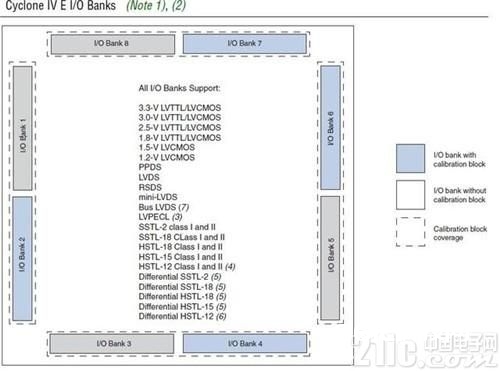

FPGA的IOE按组分类,每组都能够独立地支撑不同的I/O规范,经过软件的灵敏装备,可匹配不同的电器规范与IO物理特性,并且能够调整驱动电流的巨细,能够改变上/下拉电阻,CycloneIV设备有8个IOblank(组),见下图:

CycloneIV设备的IO组

2.2 LAB

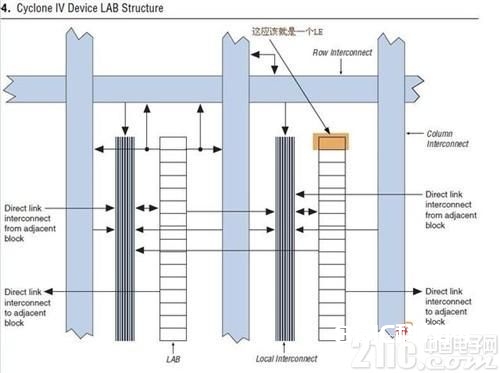

LAB是FPGA的根本逻辑单元,其实践的数量和特性根据所选用的器材的不同而不同,EP4CE115F29设备的每个LAB的布局包含16个LE、LAB操控信号、LEcarrychains、Registerchains和Localinterconnect,其LAB结构图如下:

LAB结构图

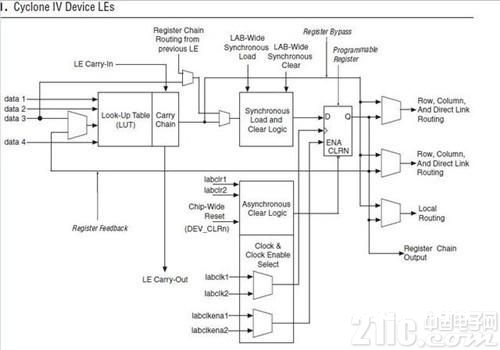

LE是CycloneIV设备最小的逻辑单元,每个LE首要有LUT和寄存器组成的,

LE的结构图

查找表LUT(Look-Up-Table)其本质是一个静态存储器SRAM,现在FPGA多选用4输入的LUT,每个LUT能够看作一个有4位地址线的16×1的RAM。当咱们经过原理图或HDL言语描绘了一个逻辑电路后,FPGA开发软件会主动核算逻辑电路的一切或许的成果,并把成果事前写入RAM。这样,在FPGA作业时,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

LUT的完成原理图