跟着计算机网络化和微机分级分布式运用体系的开展,通讯的功用越来越重要。通讯是指计算机与外界的信息传输,既包括计算机与计算机之间的传输,也包括计算机与外部设备,如终端、打印机和磁盘等设备之间的传输。在通讯领域内,数据通讯中按每次传送的数据位数,通讯方法可分为:并行通讯和串行通讯。

串行通讯是指运用一条数据线,将数据一位一位地顺次传输,每一位数据占有一个固定的时刻长度。其只需求少量几条线就能够在体系间交流信息,特别适用于计算机与计算机、计算机与外设之间的远距离通讯。串口通讯时,发送和接纳到的每一个字符实际上都是一次一位的传送的,每一位为1或许为0。

MIPI D‘Phy是一种物理上的串行通讯层,用于衔接运用处理器与显示器或照相机,作为物理层,它具有诸多方面的优势。

MIPI(移动职业处理器接口)联盟是一个非赢利安排,致力于树立移动设备中的软硬件接口标准。它的愿景是为移动和受移动影响的产品开发全球最全面的接口标准集,然后最大程度地进步规划复用率、驱动立异、缩短产品上市时刻,并有助于进步各家公司推出的产品间的互操作性。

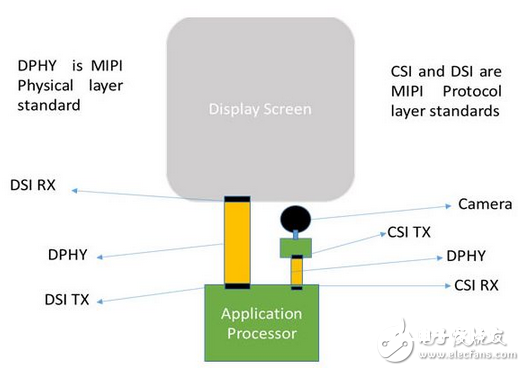

手机中照相机和显示器与运用处理器的衔接框图

MIPI D’Phy是一种物理性串行数据通讯层,上面运转着像CSI(照相机串行接口)和DSI(显示器串行接口)这样的协议。它在物理上衔接着相机传感器和运用处理器(针对CSI)以及运用处理器和显示器(针对DSI),如上图所示。

D‘Phy是一种高速、低功耗的源同步物理层,由于选用了高成效规划,因而十分合适功耗大的电池供电设备运用。它里边一同包括了有助于完结高成效的高速模块和低功耗模块。载荷数据(图画数据)运用高速模块,操控和状况信息的发送(在照相机/显示器和运用处理器之间)运用的是低功耗模块(运用低频信号)。它具有在单个数据包脉冲中发送高速和低功耗数据的特别才能。低功耗模块有助于节约功耗,高速模块则有助于完结高清晰度相片质量数据信号要求的较高带宽。

D’Phy的架构

为了满意高清质量图画的高带宽要求,MIPI D‘Phy包括有一个时钟通道和数量可设置(最多4个通道)的数据通道。经过添加数据通道数量就能够到达添加带宽的意图。经过添加通道数量,相同数量的数据在多个通道上传输能够花更短的时刻。MIPI D’Phy运用正向源同步时钟,D‘Phy接纳器的一切数据通道都用这个时钟捕获高速数据信号。

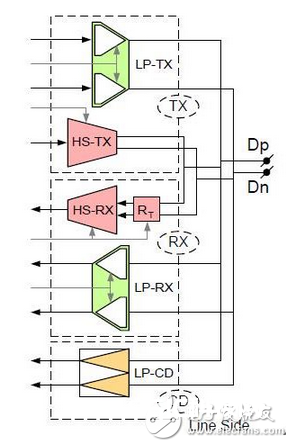

通用的D’Phy通道

为了一同满意低功耗和高速度要求,通用型D‘Phy IP(如上图所示)的每个数据通道由低功耗发送器(LP-TX)、高速发送器(HS-TX)、用于发送MIPI D’Phy特别图画的串化器组成,接纳侧由低功耗接纳器(LPRX)、高速接纳器(HS-RX)、解串器和用于接纳这些MIPI D‘Phy特别数据信号的低功耗竞赛检测器(LP-CD)组成。

时钟通道由低功耗发送器(LP-TX)、用于发送MIPI D’Phy特别时钟通道图画的高速发送器(HS-TX)组成,接纳侧由低功耗接纳器(LP RX)、高速接纳器(HS-RX)和用于接纳这些MIPI D‘Phy特别时钟信号的低功耗竞赛检测器(LP-CD)组成。

接纳器的每个数据通道(或时钟通道)经过两根导线Dp和Dn (或Clkp和Clkn)衔接到发送器。高速和低功耗数据传输都在这两根衔接着这两大通讯模块的导线上进行。

低功耗模块是一种未端接的模块,作业在单端方法,运用1.2V的逻辑电压。用于供给操控和状况信息的低功耗信号的数据速率不到10Mbps。

高速模块作业在差分方法。它们运用低电压摆幅的载荷数据信号传送信息(高速信号——Dp–Dn——的典型差分输出摆幅是200mV)。这种模块通常在裸片上有端接,在Dp和Dn之间,其典型值为100Ω。

D’Phy的作业原理以及相机输出到MIPI D‘Phy接纳器之间的数据活动

相机传感器捕获的图画数据经MIPI发送器处理后在多个数据通道上传输。用于数据传输的数据通道数量是可装备的。

发送器依据用于数据传输的数据通道数量对图画数据加以安排。然后发送器对每个通道上的数据进行串行化,并发给相应的接纳通道。

举例来说,假如用了两个通道,那么载荷数据的第一个字节在数据通道0上发送,第二个字节在数据通道1上发送。相同在接纳侧,来自每个数据通道的串行数据在D’Phy的每个接纳通道中运用的解串器协助下转化为字节格局。然后由CSI操控器将来自每个通道解串后的字节合并到一同。

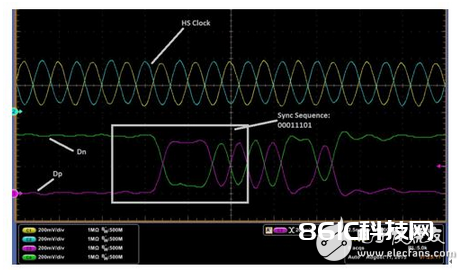

在每个高速载荷数据脉冲出现在每个通道上之前,发送的D‘Phy都会刺进一个同步序列(00011101),如下图所示。这个同步序列被接纳D’Phy的数据通道用来树立与高速载荷数据的同步。只有当同步信号被接纳D‘Phy正确解码时,载荷数据才会转发给MIPI CSI 2操控器,完结对数据的进一步处理。

发送图画中的同步序列

作为D’Phy初始化的一部分,开端一切通道坚持在LP11状况(1.2V电平)一段特定的时刻。这个LP11状况也被称为中止状况。在这之后,为了发送图画数据,发送器会向接纳器发送一个特定的序列,使接纳器通道从低功耗形式进入高速形式。高速进入序列包括在接纳器通道上驱动LP11-》LP01-》LP00 (LP-》HS转化),如下图所示。在成功接纳这个序列后,高速接纳器模块激活其终端接纳高速差分数据。

现在高速接纳器终端变成激活状况,接纳器开端接纳来自发送器的高速数据。但是,在经过LP-》HS转化后,发送器会在一段特定时刻内发送HS Zeros (V(Dn)》V(Dp)),用于保证在任何载荷数据被发送前接纳器被正确地激活。

一旦接纳器被激活,高速接纳器会继续地接纳数据,直到在它的通道上遇到LP11状况。LP11状况会将数据通道从高速形式带回到低功耗形式。

数据通道上的高速脉冲描绘了LP到HS的转化以及HS Zero

经过D‘Phy数据通道发送的载荷数据选用的是数据包的格局。它能够是长的数据包,也能够是短的数据包。长数据包包括32位的包头、有效载荷数据和16位的数据包脚注。短数据包只包括32位的包头。

在每次高速脉冲串往后数据通道都会进入LP11状况。单个高速脉冲代表对应于一幅图画水平线上的数据,而高速脉冲之间的LP11状况代表消隐期间。由于低功耗指令要求信号以较低的频率发送,因而D’Phy在低功耗和高速形式之间的这种间歇运动有助于下降总的功耗。

当没有数据需求传输时,一切通道都坚持在ULPS状况(超低功耗形式)。这是一种特别的低功耗形式,有助于进一步下降功耗。ULPS状况是经过特定的低功耗形式进入的。一旦处于ULPS状况,一切通道都被驱动到低电平(0V)。时钟通道和数据通道的ULPS进入形式是不同的。

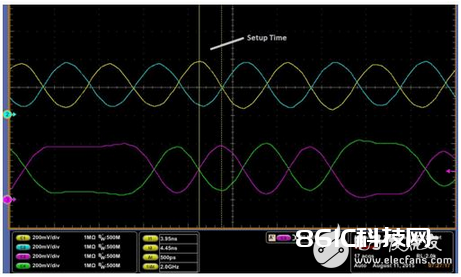

差分时钟和数据之间的时序联系

来自发送器的高速载荷数据在高速差分时钟(DDR时钟)的两个边缘传送,如下图所示。发送器传送的高速差分时钟和数据在相位上差90度,数据先发送。时钟和数据之间的这种时序联系有助于完结接纳器数据通道对树立和坚持时刻的要求。

时钟和数据之间的时序联系

本文小结

作为物理串行通讯层的MIPI D‘Phy具有低功耗作业的特性,因而对今日功耗较大的移动运用以及与移动有关的运用来说吸引力越来越大。