FPGA的作业速度越来越快,规划越来越大。使用日积月累的FPGA 正变得 愈加具有低成本高效益。由于传统 的ASIC 成本已上升得十分高, 对规划师而言,FPGA 的低成本高效益是一个十分好的音讯。不管你是领略过规划“黑暗面” 的ASIC用户, 仍是现已使用了多年的FPGA, 你现在需求在FPGA规划流程中,处理速度更快,规划更大,功用更多的FPGA。

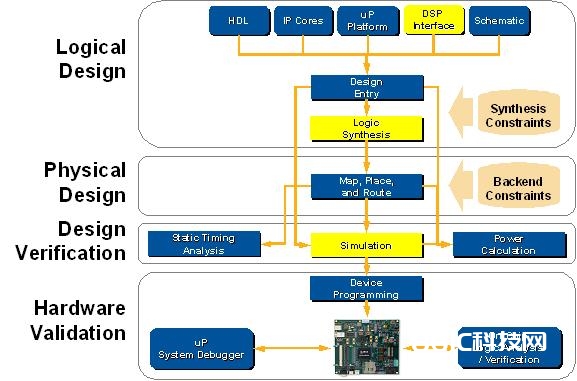

FPGA规划流程(图1 )包含逻辑规划和物理规划,规划验证和硬件验证。一些FPGA厂商只供给厂商专有的规划东西,而另一些FPGA厂商则供给第三方东西和厂商专有东西的组合。第三方东西首要用于“前端”的归纳和仿真,而厂商的专有东西专心于 “后端”的物理规划和硬件验证。

图1 FPGA规划流程

逻辑规划

逻辑规划包含简直能用于一切使用的各种输入方法,如VHDL、Verilog、知识产权核、嵌入式处理器,顶层电路图和DSP模块。

图1中的规划输入是简化的示意图,这个阶段也或许需求HDL Linting (查看是否违背语法规矩,优选的代码风格,以及规划规划)。在规划的前期阶段还能够进行I / O规划,针对团队协作的规划区分,前期静态时序剖析和功率核算等。

物理规划

跟着规划规划进程的进行,增加的物理束缚会影响映射,布局和布线。物理规划看起来比较直观,但是,这个阶段中要满意时序要求,以及增加要害功用以发生所需的体系解决方案,因而验证是至关重要的。

规划验证和硬件验证

一旦规划完结,问题就转换成,这个规划是否能正常作业?规划验证东西包含静态时序剖析,时序仿真和功耗核算,这些东西用来保证树立和坚持时刻满意时序要求,要害途径满意功用要求,以及电源供给足以满意体系功耗等等。假如规划不能正常作业,还有更多的东西可用来进行逻辑剖析,乃至软件代码调试。

挑选正确的FPGA规划东西

挑选规划东西时,决议的部分要素是所选的芯片,由于规划流程的物理( “后端” )部分总是芯片供给商专有的。但是,做挑选规划东西的决议时,还应该仔细评价归纳和仿真东西(“前端”)的功用和功用。

具有第三方归纳和仿真东西的FPGA规划东西套件能够为用户供给更高的价值。针对前端规划使命的第三方东西通常是优异的,由于EDA供给商致力于以下几个方面的尽力:

专心于规划东西

为了坚持竞争力,有必要不断完善他们的东西

依据对EDA商场的广泛和全面的了解,以及客户的需求来规划东西

有必要供给习惯不同规划流程要求的东西

例如,在莱迪思的ispLEVER规划东西套件中,咱们挑选了第三方东西完成归纳,以及功用和时序仿真。现在,该莱迪思东西套件包含Synplify ®的专业版别和Aldec Active-HDL的莱迪思版别。

第三方东西的长处

Synplify Pro

莱迪思软件中集成的Synplify Pro是一种先进的FPGA归纳的解决方案,供给优异的功用和高效率的规划。该东西还包含Synplicity的HDL剖析东西,使用户能够快速的进行调试和改善Verilog或VHDL代码。该东西为用户供给RTL 或门级的图形表明,并能够在RTL和图形表明之间进行穿插定位。

Active-HDL

在Aldec Active-HDL的莱迪思版别中,能够在单个规划中进行VHDL和Verilog的混合仿真。此外,项目办理,规划输入(包含言语帮手、层次化显现,脚本生成和测验渠道生成)以及调试和剖析东西(如代码盯梢,断点办理,波形修改和阅读)都集成在这个验证渠道。

定论

在归纳和仿真方面,EDA供给商是公认的专家;而在物理规划和硬件验证方面,只要FPGA厂商能规划和供给为芯片专门优化的后端东西。咱们的经历是借助于抢先EDA供给商的专业技术使FPGA规划东西套件为用户供给更高的价值。