10.7典型实例17:USB2.0接口的规划与完结

10.7.1实例的内容及方针

1.实例的主要内容

本节旨在规划完结了FPGA经过FX2USB2.0接口芯片与PC机进行高速数据通讯,分为读数据、写数据和读写数据3部分内容。协助读者进一步了解USB接口芯片的作业原理和规划办法。

2.实例方针

经过本实例,读者应抵达如下方针。

·了解FX2CY7C68013芯片的作业原理和SlaveFIFO形式时序。

·了解FX2的固件规划以及USB驱动程序规划。

·熟练掌握状况机的运用。

·完结FPGA与PC机之间的USB接口通讯。

10.7.2USB接口通讯实战进程

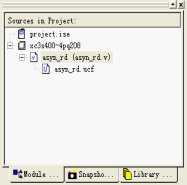

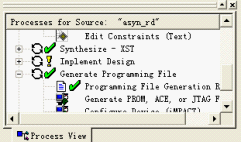

首要创立工程并为工程增加文件,如图10.30所示。

然后编译工程并下载至硬件,如图10.31所示。

图10.30创立工程并增加文件 图10.31编译工程并下载

接下来能够加载固件了,固件程序的载入有两种办法。

(1)经过芯片的I2C总线衔接外部的EEPROM,固件代码事前经过烧写器写入EEPROM中,USB设备上电运行时,经过I2C总线将EEPROM中固件代码载入。EZ-USB支撑外部EEPROM经过总线来下载固件,这种办法使开发者能够从外围硬件来下载8051程序代码,可是不利于在设备开发阶段运用。

(2)运用该芯片特有软装备功用,将固件程序存储在计算机中,当该设备接入USB电缆时,因为EZ-USB具有从头枚举的才能,所以在初始化枚举今后,用户只需要经过Cypress公司供给的开发软件USBControlPanel中Download项,就能够将固件载入到操控芯片中。该办法完全是软操作,不需要额定的硬件设备,便利程序的修正调试。

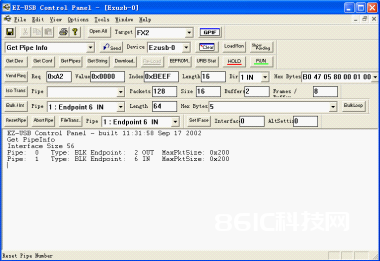

运用USBControlPanel进行固件程序下载的界面如图10.32所示。

图10.32USBControlPanel界面

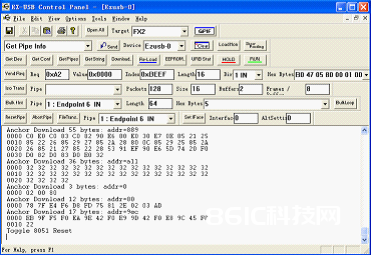

单击“Download…”按钮,挑选“slavefifo.hex”。下载固件成功今后显现如图10.33信息。

图10.33下载固件程序

其间,经过单击“GetPipes”按钮能够检查通道信息。

现在固件程序后,即可进行USB通讯测验。

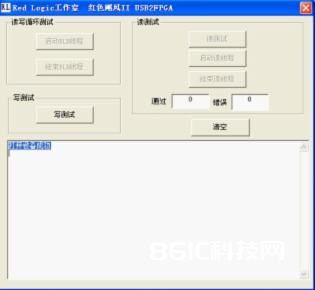

依据不同的程序,挑选相应的测验软件,测验USB接口的传输速度。如图10.34所示是RedLogic作业室供给的根据赤色飓风II的USB测验软件。

图10.34USB测验软件

10.7.3USB接口通讯实例成果

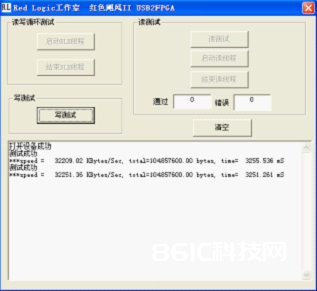

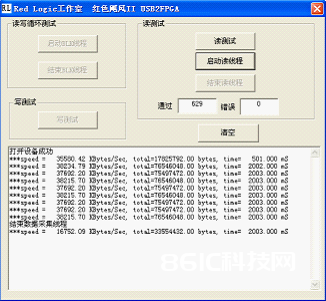

完结FPGA与PC机之间的USB通讯,并且在PC机的超级终端上面测验USB的读写速度,如图10.35和图10.36所示。关于EZ-USB的具体内容,可拜见工程文件夹中供给的相关文档。

图10.35USB测验成果

图10.36USB测验成果

10.7.4FPGA代码的规划完结

本程序功用是合作CY68013的SlaveFIFO接口时序。它完结接纳从主机下传的60KB数据,写入板上SRAM里,然后从板上SRAM中读出,再上传至主机。整个传输进程经过CY68013的SlaveFIFO来交互。

整个程序由一个状况机构成,包含以下状况:

ParameterIDLE=H0,

READ_EVENT=H1,

POINT_TO_OUT_FIFO=H2,

DATA_READY=H3,

READ_INTERVAL=H4,

READ=H5,

READ_END=H6,

WRITE_EVENT=H7,

POINT_TO_IN_FIFO=H8,

WRITE_READY=H9,

WRITE=HA,

WRITE_END=HB;

每个状况的效果描绘如下。

·IDLE:整个操作进程(包含读SLAVEFIFO和写SLAVEFIFO)的进口。对相关的寄存器进行初始化,然后转入READ_EVENT状况,开端读SLAVEFIFO操作。

·READ_EVENT:把u_addr[1:0]置为’b00,指向输出FIFO(对应端点6),然后转入POINT_TO_OUT_FIFO状况。

·POINT_TO_OUT_FIFO:判别u_flagc是否为高(u_flagc为高指示输出FIFO为空,即输出FIFO中有数据),假如为高,则发动读进程,把u_sloe置为低,转入DATA_READY状况,第一个16位数据出现在总线上;不然阐明输出FIFO中无数据,等候。

·DATA_READY:判别u_flagc是否为高,假如为高,把u_slrd拉低,持续读取下16位数据。一起为把上一16位数据写入SRAM做预备(主要是SRAM的三态总线),一起转入READ状况,不然转入POINT_TO_OUT_FIFO,等候下一次读取进程。

·READ:把上一16位数据写入SRAM,一起把u_slrd拉高,当时16位数据读取完毕。判别是否是60KB数据,假如不是,则转入DATA_READY状况,持续读操作;不然转入READ_END状况,读操作完毕。

·READ_END:把相关寄存器置为初始态,转入WRITE_EVENT状况,开端写操作。

·POINT_TO_IN_FIFO:为从SRAM中读取数据作预备,转入WRITE_READY状况。

·WRITE_READY:判别u_flagb是否为高(u_flagb为高指示输入FIFO非满),假如为高,则发动写进程,从SRAM中读取数据并送到SLAVEFIFO总线上,把u_lswr置为低,转入WRITE状况;不然阐明输入FIFO已满,等候。

·WRITE:把u_slwr置为高,当时数据写入SLAVEFIFO。判别是否是60KB数据,假如不是,则转入WRITE_READY状况,持续写操作;不然转入WRITE_END状况,写操作完毕。

·WRITE_END:把相关寄存器置为初始态,转入IDLE状况,开端下一个60KB的读写操作。

状况机的源代码如下:

case(STATE)

IDLE:

begin

//增加RESET状况

data_wr=h0; //USB接口信号初始化

u_slwr=b1;

u_slrd=b1;

u_sloe=b1;

u_addr0=b1;

u_addr1=b1;

oe=b0;

sram_d_i=h0; //SRAM的操控信号初始化

sram_a=h3ffff;

sram_re=b1;

sram_wr=b1;

wr_flag=b0;

STATE=READ_EVENT;

end

READ_EVENT:

begin

wr_flag=b1; //设定读写标志

u_addr0=b0; //指定端点FIFO

u_addr1=b0;

STATE=POINT_TO_OUT_FIFO;

end

POINT_TO_OUT_FIFO:

begin

if(u_flagc) //假如flagc高,FIFO不空,开端读数据

begin

u_sloe=b0; //开端从FX2的端点FIFO读数据

u_slrd=b1;

STATE=DATA_READY;

end

else

begin //假如flagc为低,FIFO为空,等候FIFO有数据

u_sloe=b1; //中止从FX2的端点FIFO读数据

u_slrd=b1;

STATE=POINT_TO_OUT_FIFO;

end

end

DATA_READY:

begin

if(u_flagc) //假如flagc为高,持续读取下一个数据

begin

u_slrd=b0;

sram_a=sram_a+1; //把上一个读取的数据写入SRAM

sram_d_i=data;

sram_wr=b0;

sram_re=b1;

STATE=READ; //完结数据写入后,进入读数据状况

end

else

begin

u_slrd=b1; //假如FIFO空,回到等候状况

u_sloe=b1;

STATE=POINT_TO_OUT_FIFO;

end

end

READ:

Begin

u_slrd=b1; //完结上一个数据的SRAM写周期

sram_re=b1;

sram_wr=b1;

if(sram_a!=ADDR_FULL) //假如SRAM地址没有到最大值,持续读操作

STATE=DATA_READY;

else

STATE=READ_END; //假如SRAM地址抵达最大值,完毕读操作

end

READ_END:

begin

u_slrd=b1; //回到初始状况,预备写操作

u_sloe=b1;

u_addr0=b0;

u_addr1=b0;

sram_a=h3ffff;

STATE=WRITE_EVENT;

end

WRITE_EVENT:

begin

u_addr0=b0; //指定写数据的端点FIFO

u_addr1=b1;

oe=b1;

wr_flag=b0;

STATE=POINT_TO_IN_FIFO;

end

POINT_TO_IN_FIFO:

begin

sram_a=sram_a+1; //从SRAM中读取一个数据

sram_re=b0;

sram_wr=b1;

STATE=WRITE_READY;

end

WRITE_READY:

begin

if(u_flagb)

begin //假如FIFO不满,开端写数据到FX2的FIFO

data_wr=sram_d;

u_slwr=b0;

u_slrd=b1;

STATE=WRITE;

end

else

begin

u_slwr=b1; //假如FIFO已满,等候

u_slrd=b1;

STATE=WRITE_READY;

end

end

WRITE:

begin

u_slwr=b1;

u_slrd=b1;

if(sram_a!=ADDR_FULL)

begin

sram_a=sram_a+1; //假如SRAM地址没有抵达最大值,持续从SRAM读数据

sram_wr=b1;

sram_re=b0;

STATE=WRITE_READY;

end

else

begin

sram_a=h3ffff;//假如SRAM地址抵达最大值,复位SRAM地址,进入写完毕

sram_wr=b1;

sram_re=b1;

STATE=WRITE_END;

end

end

WRITE_END:

begin

wr_flag=b0; //完毕写FX2FIFO状况,回到初始的IDLE状况

sram_a=h3ffff;

u_addr0=b1;

u_addr1=b1;

STATE=IDLE;

end

default:

STATE=IDLE;

endcase

10.7.5小结

本节对使用USB接口芯片FX2来完结FPGA和PC机的高速数据传输做了介绍,并经过编译下载在赤色飓风的开发板上完结了预订功用。