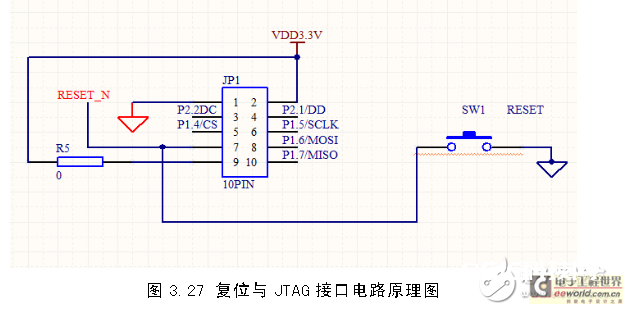

复位电路用于重新启动模块并初始化,按键开关SW1的一端接地,另一端与CC2530芯片的RESET_N管脚相连,按下按键开关SW1即可完成对电路的手动复位。

JTAG接口电路首要用来与仿真器连接到PC,完成ZigBee节点程序的下载和调试功用,一起还能够经过与电源管脚相连接对模块进行供电以及复位功用。本规划中JTAG接口的1管脚接地,2管脚与VDD相连。3管脚与CC2530芯片的P2_2管脚相连作为调试时钟信号管脚,4管脚与CC2530芯片的P2_1管脚相连作为调试数据管脚,完成将程序下载到CC2530芯片。7管脚与复位电路相连接,能够完成复位功用。