该文章叙述了S3C2440与SDRAM的地址连线剖析.

S3C2440有27根地址线ADDR[26:0],8根片选信号ngcs0-ngcs7,对应bank0-bank7,当拜访bankx的地址空间,ngcsx引脚为低电平,选中外设。

2^27=2^7 * 2^10 * 2^10 = 128Mbyte

8*128Mbyte = 1Gbyte

所以S3C2440总的寻址空间是1Gbyte。

市面上很少有32位宽度的单片SDRAM,一般挑选2片16位SDRAM扩展得到32位SDRAM.

挑选的SDARM是HY57V561620F,4Mbit * 4bank *16,共32Mbyte。

首要了解下SDRAM的寻址原理。

SDRAM内部是一个存储阵列。能够把它幻想成一个表格。和表格的检索原理相同,先指定行,再指定列,就能够精确找到所需求的存储单元。这个表格称为逻辑BANK。现在的SDRAM根本都是4个BANK。寻址的流程便是先指定BANK地址,再指定行地址,最终指定列地址。这便是SDRAM的寻址原理。存储阵列示意图如下:

检查HY57V561620F的材料,这个SDRAM有

13根行地址线 RA0-RA12

9根列地址线 CA0-CA8

2根BANK挑选线 BA0-BA1

SDRAM的地址引脚是复用的,在读写SDRAM存储单元时,操作过程是将读写的地址分两次输入到芯片中,每一次都由同一组地址线输入。两次送到芯片上去的地址别离称为行地址和列地址。它们被锁存到芯片内部的行地址锁存器和列地址锁存器。/RAS是行地址锁存信号,该信号将行地址锁存在芯片内部的行地址锁存器中;/CAS是列地址锁存信号,该信号将列地址锁存在芯片内部的列地址锁存器中。

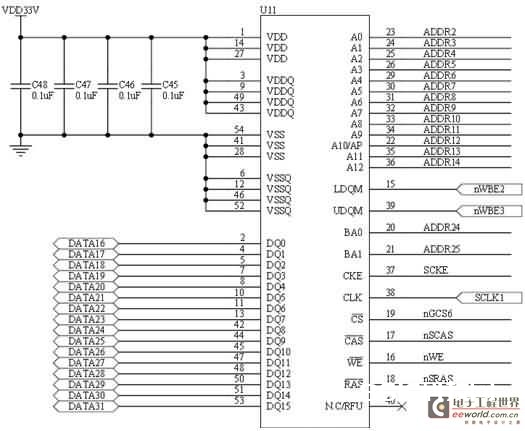

地址连线如下图:

SDRAM的A0接S3C2440的ADDR2,许多初学者都对这儿又疑问。A0为什么不接ADDR0?

要了解这种接法,首要要清楚在CPU的寻址空间中,字节(8位)是表明存储容量的仅有单位。

用2片HY57V561620F扩展成32位SDRAM,能够以为每个存储单元是4个字节。因而当它的地址线A1:A0=01时,处理器上对应的地址线应为ADDR3:ADDR2=01(由于CPU的寻址空间是以Byte为单位的)。所以SDRAM的A0引脚接到了S3C2440的ADDR2地址线上。

同理,假如用1片HY57V561620F,数据线是16位,由于一个存储单元是2个字节,这时SDRAM的A0要接到S3C2440的ADDR1上。

也便是说SDRAM的A0接S3C2440的哪一根地址线是依据整个SDRAM的数据位宽来决议的。

上面的接线图上,BA0,BA1接ADDR24,ADDR25,为什么用这两根地址线呢?

BA0~BA1代表了SDRAM的最高地址位。由于CPU的寻址空间是以字节(Byte)为单位的,本系统SDRAM容量为64MByte,那就需求A25~A0(64M=2^26)地址线来寻址,所以BA1~BA0地址线应该接到2440的ADDR25~ADDR24引脚上。

13根行地址线+9根列地址线 = 22根。别的HY57V561620F一个存储单元是2个字节,相当于有了23根地址线。BA0,BA1是最高地址位,所以应该接在ADDR24,ADDR25上。

也便是说SDRAM的BA0,BA1接S3C2440的哪几根地址线是依据整个SDRAM的容量来决议的。