跟着嵌入式产品的开展,各种嵌入式操作体系,以及嵌入式上层应用软件层出不穷。这就对大容量SDRAM的需求日益增强。现在用于嵌入式产品中的存储器首要有FLASH和SDRAM。FLASH作为静态存储器,被应用于寄存发动代码和操作体系内核,SDRAM作为动态存储器,被应用于寄存实时更新的数据信息。在此,选用Intel的PXA255处理器。运用32 MB的NOR FLASH作为放置发动代码和操作体系的静态存储空间,运用256 MB的SDRAM作为动态存储空问,运用2 GB的CF卡作为应用程序和数据的存储空间,并与液晶显示屏、音频、接触一同构成一个功用强大的嵌入式体系。

1 随机存储器介绍

随机存储器首要分为静态随机存储器(SRAM)、动态随机存储器(DRAM)及SDRAM。1个SRAM单元一般由4~6个晶体管组成,当这个SRAM单元被赋予O或许1的状况之后,它会坚持这个状况直到下次被赋予新的状况或许断电之后才会更改或许消失。SRAM的读写速度相对比较快,而且比较省电,可是存储1 b的信息需求4~6只晶体管。DRAM和SDRAM必须在必定的时间内不停地改写才干坚持其间存储的数据,但存储1 b的信息只需1只晶体管就可以完结。在数据读写的进程中,SRAM,DRAM及SDRAM均有不同的作业方法。DRAM和SDRAM相关于SRAM增加了多路寻址技能,即运用2个接连的周期传输地址数据,到达运用一半的地址线,以完结SRAM相同功用的意图。SDRAM相关于DRAM不只提出了多Bank的作业形式,而且SDRAM与CPU和芯片组同享时钟,芯片组可以主动地在每个时钟的上升沿发给sDRAM操控指令。

2 硬件规划方案

2.1 SDRAM作业原理

SDRAM自身是由多个Bank区域构成,对SDRAM的操作实际上是经过区域片选信号对独自Bank进行的操作。SDRAM中单个Bank的读取进程如图1所示。

(1)经过地址总线将行地址传输到地址引脚;

(2)RAS(行地址使能信号)被激活,这样行地址被传送到行地址门闩线路中;

(3)行地址解码器依据接收到的数据挑选相应的行;

(4)wE(写使能信号)引脚确认不被激活,所以SDRAM知道它不会进行写操作;

(5)列地址经过地址总线传输到地址引脚;

(6)CAS(列地址使能信号)引脚被激活,这样地址被传送到列地址门闩线路中;

(7)DQM(输出使能)引脚被激活,数据向外输出。

这就完结了一个单Bank的读操作,在读取数据的进程中队伍地址的寻址进程是经过两个时钟周期完结的,在榜首个时钟周期使能行地址,下一个时钟周期使能列地址,这就完结了地址线的复用。

SDRAM写入的进程和读取进程是根本相同的,只需求将wE信号激活。

2.2 硬件规划

关于SDRAM的硬件规划需求确认3个方面的内容:经过处理器的特性挑选SDRAM的类型;确认SDRAM地址线、数据线的衔接方法;确认SDRAM操控信号线的衔接方法。

2.2.1 SDRAM的挑选

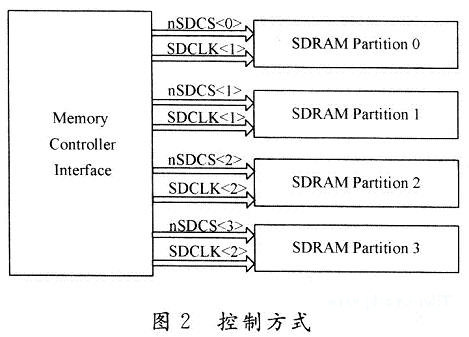

该渠道处理器挑选Intel公司XSCALE架构的PXA255,它针关于SDRAM有4根专用的动态片选信号,可以支撑4块内存区域,如图2所示。

其间每块区域所能支撑到的最大物理地址为64 MB。而且每一块内存区域均可运用16 b或32 b的SDRAM。

在硬件规划进程中考虑到硬件运用的可调理性,选用8片16 b×4 MB×4 Bank的SDRAM,共搭建了256 MB的极限存储空间。其间,SDRAM挑选类型为三星公司的K4S561632E。

2.2.2 数据线、地址线的分配

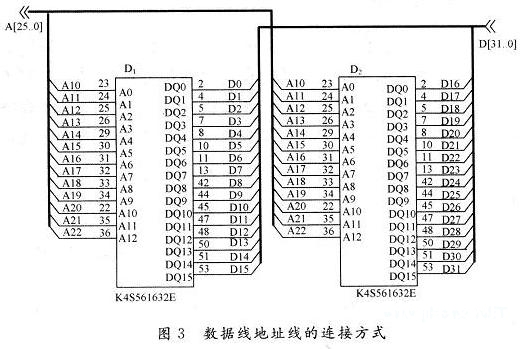

PXA255处理器共有32位数据线和26位地址线。故在硬件规划时需求并行处理2块16 b的SDRAM,别离衔接高位和低位的16根数据线。

关于地址线的衔接,首要需求参阅SDRAM的数据手册,确认SDRAM队伍地址线的个数。其次依据处理器数据手册确认具体地址线的衔接方法。

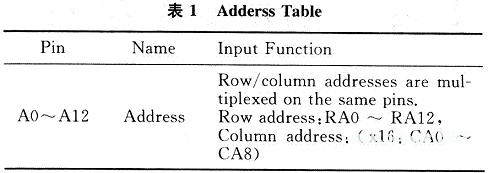

在三星K4S561632E的数据手册中是这样给出的,如表1所示。

从表1中可以得出队伍复用13根地址线,其间行地址13根,列地址9根,共组成22根地址线的寻址空间。在处理器PXA255中,给SDRAM分配的地址线空间是从A10~A22。这样就可以彻底确认地址线和数据线的衔接方法,如图3所示。

2.2.3 操控信号线的衔接方法

关于SDRAM需求确认的操控线包含时钟信号线、区域片选信号线及Bank片选信号线。关于这三类信号线PXA255处理器是这样给出的,即:

(1)每两组内存区域运用同一组时钟信号线,即每128 MB的内存空间运用同一根时钟信号线,故在规划中运用了2组时钟信号线。

(2)共有4根区域片选信号,别离操控64 MB的物理地址空间。最大支撑到256 MB的物理地址空间。

(3)地址线的23,24位用来完结对SDRAM内部Bank的挑选。

2.3 硬件的移植

针关于PXA27x系列的高端处理器,Intel并没有对SDRAM部分做本质上的改动,仍然是4根动态片选信号,故硬件方面的规划可以彻底移植到PXA27x系列的处理器中。

3 软件规划方案

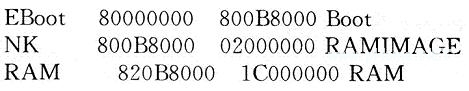

Windows CE操作体系下对内存的驱动代码首要分为两个部分,首要在BootLoader中对SDRAM进行底层初始化;其次在体系BSP包内需求将SDRAM所对应的物理地址映射为Windows CE下可以辨认的虚拟地址。

操控线的衔接方法如图4所示。

3.1 BootLoader代码的买现

BootLoader是体系运转的起始点,它包含着体系运转的榜首行代码。BootLoader自身也是一个功用完好的微型操作体系,在内部需求完结使命调度、内存办理、文件体系,以及各种必要设备驱动程序的装备。其间内存办理便是完结SDRAM初始化的作业,包含设置SDRAM作业频率、设置片选信号寄存器、设置改写距离和SDRAM潜伏期、以及装备体系内核的复制地址。操控线的衔接方法如图4所示。