画FPGA开发板所犯的那些过错,小编这儿先截下我开始画这个开发板的一张“不忍目睹”的PCB让咱们看看。

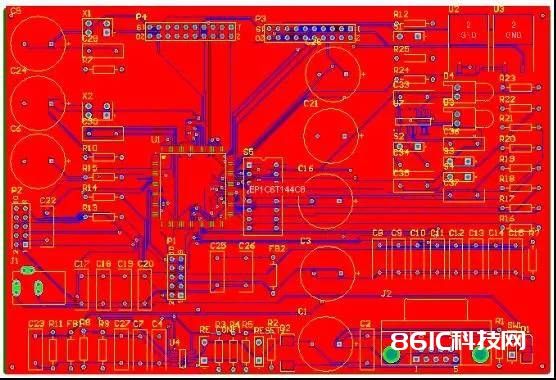

Top Layer如图:

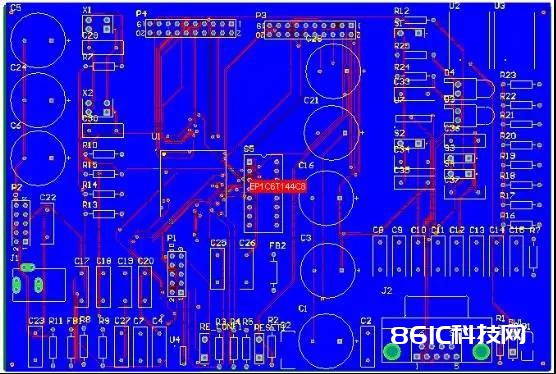

Bottom Layer如图:

第一遍画的时分,想“兵贵神速”把它画完,敷衍了事,可是等悉数布线完今后却发现这儿面的过错实在是太多了,我觉得最中心的过错便是一开始就没有留意整个体系各个元器件的布局,然后导致了“灾祸”的产生,后来的布线也就十分困难。咱们很简单能够在上图中看出布线的长度大部分都很长,其实这也是十分严峻的过错,特别关于高速信号线来说。输入、输出端用的导线应该尽量短,且尽量不要长距离的平行,当然,差分线在外。咱们知道,其实每个%&&&&&%都会有引脚电感,从芯片的引脚导线到电阻、电容和电感线圈的引线,每条线和走线都有寄生%&&&&&%和电感,它们直接影响着导线的阻抗并且对高频率灵敏。

一般来说,在低频段时导线首要出现电阻特性,而依据RF电路理论可知,在高频段时,导线会出现电感特性,我画的这个板子是25MHz的,所以能够对这个要素迷糊一点了,可是,为了避免带来不必要的费事,在走高频信号线时仍是小于150MHz波长的1/20为好,避免在板子上构成意外的搅扰源,由于当信号频率到达150MHz以上时,PCB走线就相当于“变成”了一个有用的天线了!

咱们还得留意一下差分信号的走线,很重要的一点便是差分信号线在板子上的走线有必要相同长,并且关于信号速率在一百MHz以上的,还得选用带阻抗操控的高速连接器,我画这块板子的时分不需要考虑这点,但我仍是提防了一下,趁便在这儿提一下,嘿嘿,要是今后遇到这么高的频率时,就得好好酌量了,否则会引发EMI问题喔。

不知道咱们有没有发现,在上面我画的PCB中其实蕴含着一个很好的长处,那便是整个板子的过孔很少!咱们应该都知道,在布线时,咱们应该尽量少用或许不必过孔,由于这个会带来更多的集总线模型电感,这就或许会使信号质量下降,更有甚者会引发EMI问题,那可就比较费事了。

之后我又从头好好地画了几回,再截个图看看,

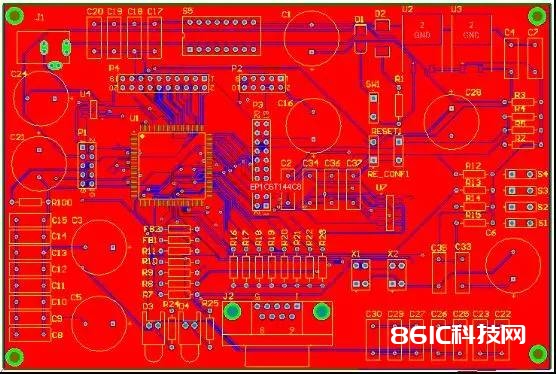

Top Layer如图:

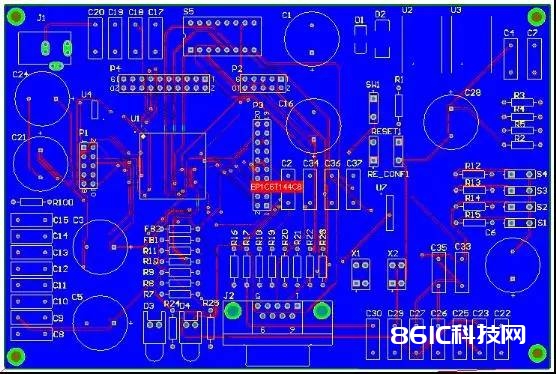

Bottom Layer如图:

感觉比第一遍画的图仍是有改善的,但必定还能够画得更好,仅仅觉得现在的话,就这个水平了,今后再渐渐练!