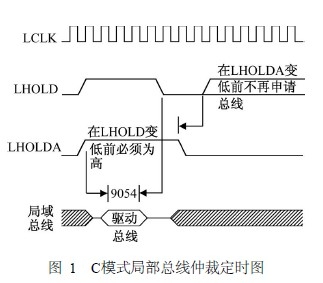

PC I总线标准十分杂乱,开发接口设备具有适当 的难度,在规划中需注意以下问题。PCI的时钟扇出 才干较差,一般只支撑2~3个负载; PC I接口逻辑复 杂, 总线的接口电路大致需求1000门的逻辑才干实 现,这些逻辑电路首要作为逻辑译码、时序操控、存放 器F IFO等。PCI总线接口逻辑的规划作业,不是一般 的中小规划TTL 或COMS电路所能完结的,所以,本 文的方针芯片选PCI9054,一起选用TMS320F2812作 为轴控芯片。PCI9054是一种多功用、多模态的接口 操控芯片,其功用装备拜见文献[ 3, 4 ]。经剖析,与 TMS320F2812总线接口时, PCI9054选C形式作业较 合适,图1是PC I9054在C形式下的守时图。

2 TMS320F2812与PC I总线接口

TMS320F2812具有外部接口XINTF, 接口具有 DMA传送才干,这是F2812与PC I9054接口的根底, 图2是F2812的PC I总线接口框图。体系中有一片共 享存储器(DMA RAM) ,它大部分时刻是F2812的外 存,而软件上把它的地址空间分为PC机和F2812“写字板”空间,经过交流总线操控权的方法交流信息。 握手信号是选用F2812 的通用输出引脚信号对接 PCI9054的USERi 运用者输入端。当F2812 答应 PCI9054占用“写字板”时,该引脚为低,此刻, PC机通 过读取PC I9054的相关存放器可探测到低电平信号, 经过PC I9054 占用F2812 总线,操作“写字板”。当 F2812不答应PC I9054占用“写字板”时,通用输出引 脚变高, PC机测知后,铺开总线, F2812从头取得“写 字板”操控权,依此方法循环作业。

3 数控体系DMA作业方法设置

为了完结DMA传送,首要需将PCI9054芯片的局 部总线设定在C形式,而F2812的外部接口XINTF以 16位方法作业,有必要进一步将PC I9054 设定为16 位 的作业形式。由图1的操控时序可知,在此形式下通 常PCI9054不驱动部分总线,相关引脚处于高阻状况。 剖析图2中地址总线和数据总线的联系可知PC I9054 与F2812是可互通的,当时数据/地址总线的操控权在 F2812手中,即挂接在总线上的DMA RAM只被F2812 所运用, 作为它的外部存储器。一旦PC 机指令 PCI9054操作部分总线, PCI9054发生总线DMA握手信 号LHOLD (高电平有用,拜见图1) ,该信号送给部分总 线处理器F2812。当F2812能够让出总线时,其总线信 号变高阻,地址和数据线让给PCI9054,完结DMA操作。

PC机经过PC I9054占用F2812的总线后,本来存 储在DMA RAM中的数据依然有用,其间包括轴控芯 片F2812发送给PC机的数据,该数据的地址及数据 意义由用户自己界说。在DMA RAM中会留有一块地 址空间用于PC机向轴控芯片传递指令和数据。当操 作结束时, PC机铺开部分总线, DMA RAM的内容在 F2812从头取得操控权后变成F2812的可用信息。依 此方法, PC机和F2812在每一个数控采样周期内进行 一次数据交流。

PC I9054的作业方法选为PCI方针形式。相对于 PC机, PC I9054 是从设备,而相对于F2812 它又变成 了主设备。

当把PC I9054设定为C方针形式下16位总线时, BE3#为高字节使能(LD [ 15: 8 ] ) ,而BE2#未用, BE1# 为地址线LA1,BE0#为低字节使能(LD [ 7: 0 ] ) 。此刻 PCI9054具有LA1 ~LA31 共31 根地址线, F2812 的 XINTF只要20根地址线,这使地址线的处理较为杂乱。 4 研磨专用数控体系握手信号和译码逻辑

(1) 译码逻辑

PC I9054 的LD 数据线信号直接与16 位的 F2812XINTF 数据线信号相连, 并驱动至存储器 CY7C1041的数据线上。而256K的CY7C1041 只需 要18根地址线,即PCI9054的LA31~LA19和A18~ A19都由译码电路处理而发生接口设备的片选信号。 译码电路见图3,按此图衔接,可完结接口的译码 功用。U1A的4个输出端别离对应4个256K的DMA RAM芯片的片选信号, 可用于挑选4 个轴控芯片 F2812,但需添加其他辅佐电路; U3 的2Y输出DMA RAM的写信号, 3Y为其读信号。U3的A /B端HOLDA 信号操控PC I9054 和F2812 的切换, 以便轮番操作 CY7C1041存储器芯片。