0 导言

FPGA(Field Programmable Gate Array)即现场可编程门阵列,跟着微电子技术的开展,FPGA的性能变的越来越优胜,运用空间也变得越来越广。FPGA具有支撑重复编程的特色,可是掉电后不能保存装备信息。因而在上电后,都需求用户将规划的FPGA装备文件从外部存储器中下载到FPGA中才干作业。针对这种状况,本文提出了一种以USB芯片,FLASH芯片和CPLD组成的FPGA主动加载体系。该体系经过USB芯片将PC中的装备文件传送给CPLD,CPLD再将其写入FLASH芯片,FLASH芯片能够持久地存储装备文件。这样FPGA每次上电后CPLD将FLASH中的装备文件读出来装备FPGA。从而使FPGA在每次上电后都能够主动获取装备文件,使其能够作为一个独立“芯片”作业,具有很强的实用性。在PS形式装备方法上也有改善,在传统PS形式下装备多个FPGA时一般运用前一级的FPGA的nCEO衔接后一级FPGA的nCE来使能后一级FPGA,这样在第一个FPGA装备好后,nCEO会使能下一级的FPGA开端装备。这样只能先装备第一个FPGA,并且不能自在操控来装备下一级的FPGA。选用CPLD一起衔接两个nCE,在前一级FPGA装备好后,获取完结信号来装备第二个FPGA,这样不受FPGA前后级联的次序影响,能够自在挑选装备FPGA。

1 体系结构及芯片简介

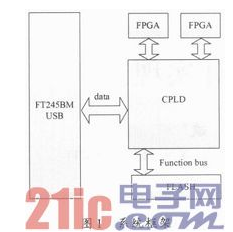

体系由CPLD,USB芯片和FLASH芯片组成,外加PC部分合作体系作业。体系结构见图1。体系中USB芯片衔接PC与CPLD,PC经过USB向CPLD发送指令来操作FLASH。首要发送擦除FLASH指令,擦除结束或将装备文件写入FLASH芯片。在FLASH芯片中能够存入多个FPGA的装备文件,在上电后或许需求加载时,CPLD读取FLASH中的装备文件并且对FPGA进行装备。

2 烧写FLASH时序

USB、CPLD和FLASH的衔接联系如图2所示。USB将PC的指令和装备文件发送给CPLD,CPLD经过时序逻辑操控FLASH。

体系中所运用的USB芯片是FTDI公司的FT245BL,将USB芯片与PC衔接后,USB芯片会主动识别为串口,运用串口调试帮手能够向其发送指令或文件。

擦除和烧写FLASH操作如下所述:

FLASH芯片选用恒忆公司的M29EW系列512MNOR型FLASH。选用异步时钟操作,时序图中的fls_byte管脚对应的位宽挑选信号,在本体系中将其拉低标明运用8 b位宽fls_adr标明地址,fls_dat标明数据,fls_cen为芯片使能信号,fls_oen为芯片读使能信号,fls_wen为芯片写使能信号。

如图3和图4所示,在履行擦除或写操作时序时,将fls_cen拉低、fls_oen拉高时能够履行写或擦除指令,fls_wen上升沿采样地址,下降沿采样数据。fls_ry_by是芯片的繁忙或闲暇信号,是FLASH芯片专一的输出信号,用于标明正在履行擦除或许写操作。

(1)擦除FLASH

在运用FALSH芯片之前需求对其进行擦除,PC经过USB向CPLD宣布擦除指令后如图3所示。写入接连5个对应的地址和数据后,FLASH芯片将整个芯片的数据擦除,如图3所示在履行后,fls_ry_by信号拉低标明进入了擦除状况。

(2)烧写FLASH

如图4所示,在履行写FLASH操作时,首要需求给出写FLASH三次对应的数据和地址作为前置指令,然后给出需求写入FLASH的地址和数据。在接到指令后,CPLD依据图中时序将FPGA的装备文件写入FLASH。

3 PS形式主动加载FPGA

FPGA的装备管脚如图5所示。

在PS形式下装备FPGA的FLASH,CPLD和FPGA的衔接联系如图5所示。

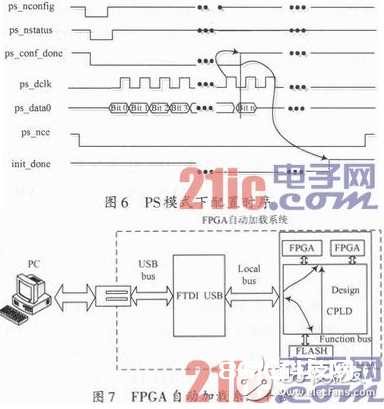

图6所示为PS形式加载FPGA的流程图。在加载进程中,将ps_nce拉低并且将ps_nconfig拉低至少40μs后再拉高,正常状况下这个操作会使ps_nstatus发生一个由低到高的一个脉冲信号并且使ps_conf_done由高变低。在ps_nstatus发生上升沿的瞬间当即给出ps_dclk和ps_data0来装备FPGA,其间ps_data0信号是经过读取FLASH芯片中的数据完结的。FPGA在接纳装备文件的进程会主动识别文件的结束,在装备结束后ps_ conf_done信号会拉高以标明装备结束,装备进程中init_done会由高变低,在经过至少18μs后init_done信号拉高标明完结初始化,随后进入用户形式。惯例的方法选用nCONFIG,nSTATUTS,CONF_DONE复用,并且前一级FPGA的nCE衔接后一级的FPGA的nCEO,这样加载次序就被固定,并且每次加载只能先加载第一个FPGA,待加载结束后才干加载第二个FPGA。与惯例的装备方法不同之处在于经过使能nCE来挑选需求装备的FPGA,给出相应的装备文件与信号ps_conf_done的时序来判别是否装备完结,这样就能够自在挑选装备FPGA。

如图7所示为FPGA主动加载的渠道,经过CPLD的逻辑操控和USB芯片的总线能够将PC端装备文件写入FLASH芯片中。在需求运用主动加载功用时,在上电后CPLD会当即读出存取在FLAHS中的FPGA装备文件,以PS形式装备相应的FPGA。

4 定论

经测验体系能够在上电后对FPGA进行主动加载。本文供给了体系的结构结构和实施方案全体流程以及时序要求,具有很强的运用和参考价值。