1 导言

数据收集是剖析模仿信号量数据的有用办法。而实时显现数据是自动化检测体系的实践需求。在测验空空导弹导引头的过程中,导引头的呼应信号包含内部二次电源信号和模仿量电压信号。检测过程中要求检测体系实时显现导引头的作业状况,显现二次电源和模仿量呼应电压信号,判别导引头功用,一起确保在十分情况下人为对导引头做出应急处理,保护导引头。关于模仿量电压信号,一般选用模数转化、过后数据标定的办法完结。依据实践需求,研发相应检测体系可作为导引头日常保护和修补的重要东西。这儿介绍一种依据单片机和CPLD的实时数据收集显现体系规划方案。

2 体系构成

该体系中待收集显现电压信号共16路,动态电压规模为-22~+27 V。因为这些电压信号改变频率较低,或许以为频率无改变,且检测体系只关怀其电压值,所以在低采样率下就可满意体系要求。依据需求,体系规划的采样率即显现改写速率在1.56 k/s以上。

选用单片机80C196KB和可编程逻辑器材EPM7128SLC为中心操控器,以80C196KB内部集成A/D转化器作为模数转化器完结16路电压信号的实时数据收集、显现、操控。该体系总体规划结构框图如图1所示。

整个体系首要由信号预处理、信号选通、单片机收集、双机数据传输以及数据处理显现等模块构成。其间,信号选通模块由CPLD和多路模仿选择器组成。

3 体系硬件电路规划

3.1 信号预处理电路

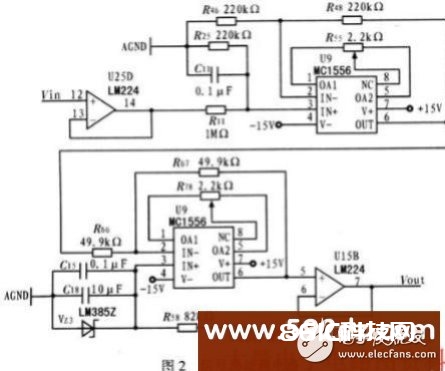

因为待收集电压信号输入动态规模较宽,且极性各异,关于单片机A/D转化器来说,需求调度到可以收集的电压规模闱0~5 V,所以要一致调度收集信号,如图2所示。

图2中运放LM224和MC1556均选用双电压供电,以进步动态信号输入规模;电阻均选用精度为0.1%的精细型金属膜电阻,以进步电压转化精度。

在二级电压凋理过程中,MC1556同相输人端选用稳压电路以削减长期通电情况下温度升高对体系发生的不良影响。南于电压跟从用具有输入阻抗大和输出驱动能力强的特色,故在预处理电路的输入端和输出端均选用电压跟从电路。

3.2 信号选通电路

ADG508A是一款8通道CMOS模仿多路选择器,具有高速转化速度和低内阻特性,通道切换具有防短路功用。在CPLD操控下,它可对收集信号进行有序通道切换,合作单片机进行数据收集。

EPM7128SLC是一款Ahera公司出产的CPLD,其容量为128个宏单元,选用硬件描绘言语VHDL对CPLD编程设置完结信号的选通操控。首要编写分频器模块对1 MHz晶体振荡器进行20分频,输出2路相位相错、周期为20 μs的矩形同步信号。其间一路信号经D触发器进行2分频,得到占空比50%、周期为40μs的方波信号;然后编写信号选通操控模块。此模块依据方波信号和另一路同步信号循环输出操控信号,两模块都在MuxPlus-II环境下开发,CPLD操控信号时序仿真成果如图3所示,其间,信号FRM和ROAD是单片机主程序运转的勤务信号;CS1和CS2是2片ADG508A的片选信号:A0、A1和A2则是ADG508A通道选通操控信号。

3.3 单片机收集电路

80C196KB是Intel公司出产的一款16位CMOS单片机,片内集成有8路A/D转化器,该转化器包含一个8通道多路模仿开关,采样坚持电路和10位A/D转化器。因为该体系外部有多路选择器,故内部无需通道转化,选用一个ACH0通道即可完结数据收集。关于选用12 MHz晶振的单片机体系,完结一次A/D转化需22μs。80C196KB的A/D转化器选用逐次迫临的办法完结模仿量到数字量的转化,基准电压设定十分要害,内部阻容网络将基准电压Vref等分为1 024个阶梯,每级为Vref/1 024 V。经过与基准电压比较,可得到10位数据转化成果,其间基准电压的精度以及安稳度直接影响到丈量成果的肯定精度。因此在电路中Vref选用独自电源供电并经过基准稳压源如LM136的5 V进步精度及安稳度。

80C196KB经过判别ROAD信号在其上升沿读取前次A/D转化成果,一起发动A/D转化器转化下一路信号,该单片机用FRM信号作为非屏蔽中止使计数器DXL归零,主程序循环一次,确保对16路通道信号的时分复用收集。单片机80C196KB程序流程如图4所示。

3.4 双机数据传输

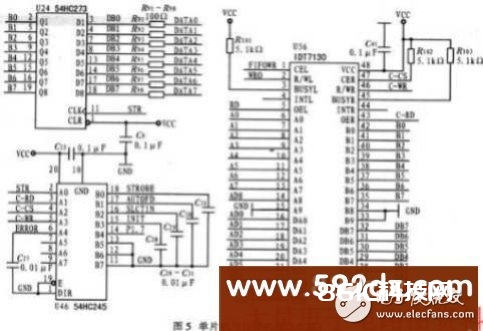

为到达收集数据的实时可控性,体系规划双机通讯接口作为单片机A/D转化数据向核算机传输的通道。核算机选用WDM下的EPP形式通讯,速度达500 KB/s~2 MB/s。运用双端口RAM IDT7130作为首要元件,经过通讯接口,单片机将A/D转化数据存入双端口RAM中,核算机则实时显现从双端口RAM中读取的数据。单片机经过双端口RAM IDT7130的A端口进行写操作,核算机则经过B端口进行读操作。握手信号由单片机经过对ROAD信号计数发生,二者可异步读写操作,完结数据交换。图5为单片机与核算机接口电路。

4 体系软件规划

4.1 数据标定

在给定Vref=5 V,设单片机收集端口输入电压为Vin与之相对应的A/D转化数字量为X,则X=1 024 Vin/5V。关于线性变换预处理电路可选用Y=5KX/1 024,其间,Y表明电压实测值,X表明与Y对应的A/D转化值,K为放大器增益。令K=Ymax/5 V,其间Ymax表明待丈量电压的最大值。为确保收集精度,应先核算Ymax,以坚持满意的A/D转化有用数字。以待收集电压0~27 V为例,预处理电路增益为27/5=5.4。

4.2 实时显现

读数及显现软件在VC++6.0环境下编写,运用对话框形式,并口选用WDM驱动方法。软件运转时直接翻开驱动设备,一起运用AfxBeginThread()函数生成一个新线程,其操控线程函数实时更新读取并显现数据。因为单片机选用1O位A/D转化器,所以一次转化成果分两次传输,分别为高位和低位传输。并口数据传输也选用8位方法。上位机在读取数据后,2组数据经移位、加法运算后得出一个完好数据,标定后在核算机界面显现。

5 定论

实践证明,该实时收集显现体系彻底满意导引头的检测需求。收集电压精度可达mV级,改写率在1.56 k/s以上。该体系选用单片机和CPLD技能,电路规划结构简略,实践运用可靠性高、通用性强、运用灵敏,且收集通道具有扩展性。但在电路规划过程中应留意:因为体系既有模仿电路又有数字电路,所以合理布线对体系至关重要,应采纳合理布线措施以确保基准地线的安稳性,然后进步收集精度。