在产业化出产的今日,测验程序的运转时刻直接关系到测验的本钱,一般芯片规划越大,所需测验的向量就越多,测验时刻也越长。考虑到出产本钱,芯片很多出产时,削减整个测验程序的运转时刻是下降测验本钱的要害(就当今许多最先进的集成电路而言,测验本钱已占到总本钱的30% 一40%)。因而,这就需求优化测验程序,使其既有较高的毛病覆盖率,又能够快速、高效地测验。优化测验程序时,削减测验时刻在这方面将起到严重的效果。

优化直流参数测验程序

HiLEVEL公司的ETs77O测验体系每履行一次.set(履行)文件,就需调用一个.tn1(向量)文件。而调用.tⅡl文件所需的履行时刻远大于调用.set文件。这样.仃n文件容量的巨细直接影响测验程序的运转时刻。因而在测验直流参数时,最好独自调制一个测验向量,只供测验直流参数运用。此测验向量的容量越少越好,只需包括所测验管脚要求的状况即可。这样在调用向量文件时,能够节约时刻。像82c51的功用测验有上万条的测验向量而直流参数的测验向量只需求几十条就能够完结悉数直流参数测验(调用过万条的向量文件需求522ms,而调用十条以内的向量文件则只需求90ms)。

在测验直流参数时,削减测验时刻的主导思维便是将串行测验办法改为并行测验办法,一同丈量多个管脚的直流参数要比逐个测验单个管脚的直流参数节约时刻。以82C51电路为例,在测验其数据总线的输出高电平时,八个管脚一同测验花费的时刻为126ms,假如独自测验每一个管脚,八个管脚悉数测验完结大约需求4o0ms。但一同丈量多个管脚的直流参数需求两个条件:①每个测验管脚对应的测验通道都具有独立的驱动测验才能;②适宜的功用测验向量将这些管脚一同设置到必定的状况。

ETS77O测验体系彻底能够满意条件①的要求,而条件②是对测验程序规划者提出的要求,需求在调试测验向量时,提早考虑到这一点。尽量使多个管脚能够停在同一状况,82c5l测验直流参数的详细办法是将0地址写全“0”数据,FF地址写全“l”数据。这样,在读0地址数据时,数据总线的输出状况为全“O”,能够测验有关低电平的一切直流参数。在读FF地址数据时,数据总线的输出状况为全“l”,能够测验有关高电平的一切直流参数。这样在测验直流参数时,数据总线都停在同一状况,能够一同完结对不同管脚的电参数的测验,并且测验向量只需几条就可完结,这样又能够削减调用.tn1文件的时刻,一箭双雕。别的,在不同的测验体系上有不同的节约测验时刻的办法。就现在正在运用的ETs77O测验体系,在测验直流参数时,还能够运用许多小细节来完善程序,削减测验时刻,下降测验本钱。如在测验漏电流和电源电流时,依据规范所要

求值的巨细挑选适宜的量程,即在测验程序中激活Rangs对话框,挑选适宜的规模。由于,测验体系在测验漏电流和电源电流时,假如不激活Rangs对话框,体系默许参阅值与丈量值相比较,以固定差值逐步向丈量值迫临,得出实测值。这样很浪费时刻,假如设定了量程,体系依据量程设定参阅值与丈量值相比较,以固定差值逐步向丈量值迫临,很快就能够得出实测值。如82c5l电路的输入高电平电流规范要求应在±1O A,假如激活Rangs对话框,并挑选20 A这一挡,测验时花费的测验时刻大约为2O9ms,而不激活Rangs对话框,直接测验则需求花费的测验时刻约为1170ms。依此类推在测验输人低电平电流和电源电流时相同都激活Rangs对话框要比不激活Rangs对话框节约很多的测验时刻。82C5l仅为28管脚的电路,关于上百管脚的电路而言,优化直流参数的测验程序,削减的测验时刻更为显着,有些电路测验程序经过优化后,测验时刻仅为优化前的三分之一乃至更少。

优化沟通参数测验程序

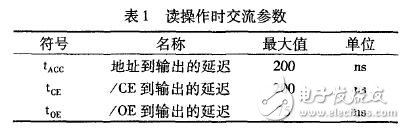

现在,遍及运用的沟通测验办法主要有两种:查找法和功用验证法。就两种测验办法而言,各有优缺点。运用查找法测验沟通参数简略易学,能够得到确认的参数值,但测验时刻长,适合在芯片的研发过程中运用,了解器材的详细参数值,对规划和修正工艺参数供给参阅。但在大规划出产过程中,整个流程都相对安稳牢靠,就没必要运用这种办法了。此刻,功用验证法就显现出它的长处。功用验证法并不是真实去i贝4试和显现器材的沟通参数,而是选用守时判别的办法来确认沟通参数是否在合格规模之内,能够理解为进行了一次具有守时精度的高速逻辑功用测验。这样在功用测验的一同,就能够完结沟通参数的测验,不必再逐个测验沟通参数,削减了很多的测验时刻,到达下降测验本钱的意图。以27cl28—2O为例,叙述测验沟通参数的详细办法。27c128—2O读操作的沟通测验波形如图1所示,参数如表l所示。

在编制功用测验程序时,按要求给出输人、输出值,测验频率f=1MHz。地址输入端选用NRz调制,延迟时刻为1Ons。/cE、/OE选用R0ne调制,/cE的延迟时刻为l0ns,而/OE 的延迟时刻为135ns。数据输出端的比较时刻为2l0ns。在测验

时,/cE、/OE的测验向量一向为0,这样经过调制的波形与上述波形共同。在测验体系上对其功用进行测验,若测验经过,则电路满意参数手册的要求,说明晰所测值在合理规模内。运用查找法测验每一项参数的延迟时刻大约需求534ms,而27c128—20读操作的延迟时刻就有3项,假如运用查找法测验以上三项参数,就需求l6O2ms。而运用功用验证规律彻底省去这些测验时刻。相同写操作的沟通参数还有约l0项,假如相同都运用功用验证法,则能够省去很多的测验时刻。但功用验证法测验沟通参数,要求测验编程人员适当了解器材的功用和各种参数要求及测验体系的测验原理,才能使功用测验与沟通参数测验完美结合。

优化链接程序

ETS770测验体系在测验时,需求将每一个独立的.set文件连接起来构成一套完好的测验程序。而将独自的已调试经过的测验程序逐个链接时,也有必定的技巧。在链接时尽量将同一文件名的.tm文件链接到一同,这样体系在前一级调用.tm文件后,假如文件名相同,则不必再从头调用此文件,而是直接默许前一级文件。默许上一级的.tHl文件测验向量有上万条的也只需求47ms,而从头调用新的.tm文件即使是只要十条也需求90ms。

结束语

现代社会是个科技开展一日千里,出产一日千里的年代。集成电路还在按着摩尔定律的办法开展,整个测验程序的运转时刻约束着测验本钱,优化测验程序已成为火烧眉毛的问题。以上介绍的几种优化测验程序的办法,假如能在测验程序中一同运用,能够削减很多的测验时刻,下降测验本钱。