在科学研究、通讯和一些自动操控中,常常需求精确守时的接连脉冲信号,用于发生测验信号或操控用的时序。脉冲推迟的根本办法可分为数字办法和模仿办法。数字办法选用计数器或存储器完结推迟操控,其缺陷是无法满意高分辨率的要求;模仿办法选用专用的脉冲推迟器材完结推迟操控,其缺陷是抗干扰效果欠好,简单发生颤动和电压不稳等问题。所以咱们提出构建数模结合的体系,完结接连脉冲信号的高分辨率推迟。

1 体系功用

本体系拟定对频率规模在1~50 kHz左右的TTL电平脉冲序列进行多路推迟处理。各路推迟时刻别离由单片机动态设定,最大推迟时刻为1 ms,最大分辨率为0.15 ns级。

2 计划挑选

由于所要处理的脉冲序列的脉冲间隔时刻大于脉冲推迟时刻,不用考虑多脉冲存储和再生的问题,所以数字办法中选用计数器法,完结推迟量高位部分操控。现存的计数器体系计划大多是根据SRAM的FPGA,其缺陷是SRAM中的程序掉电后易丢掉,上电后要借助于外围的单片机从头向SRAM中写程序,影响了体系的反应速度。为了处理这一问题,体系选用Actel公司的Flash FPGA,掉电后程序不易丢掉,进步了体系的反应速度。别的,FPGA中的PLL模块能对外部时钟源进行分频、倍频,给计数器模块供给触发和计数脉冲。这些大大减少了芯片数目,进步了集成度,节省了体系面积和本钱。然后,用VHDL语言对FPGA进行编程,完结硬件电路软件化规划,操控各路时序,完结用数字办法对脉冲信号的推迟操控,此刻分辨率能够抵达10 ns级。

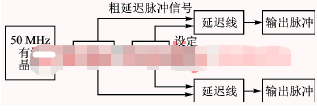

用模仿办法进行推迟低位部分操控时,选用了DS1020推迟线芯片。只要在电路板上建立多组以DS1020推迟线芯片为主的电路,就能够一起输出多路脉冲序列。此刻最大推迟分辨率能够抵达0.15 ns级。本计划中各路计数器模块和推迟线的推迟时刻均可由MCU编程来动态调整,体系结构框图如图1所示。

图1 体系结构框图

3 计划完结

体系选用Actel公司的ProASIC3 A3P250芯片完结数字部分。体系时钟由外部50 MHz晶振供给,时钟引脚衔接到FPGA的CCC大局时钟引脚上;频率能够通过FPGA内部的PLL完结倍频和分频,设定需求的频率。由于在多路脉冲推迟计划中电路的同步是确保操控精确的条件,所以应该首先为电路供给一个基准脉冲。通过PLL将50 MHz的频率倍频,发生一个100 MHz的低频触发脉冲,然后触发各路计数模块开端计数。一起,将100 MHz通过另一计数器模块得到1 kHz的触发脉冲,此刻能够根据需求推迟的规模通过MCU编程来设定各计数器的初值,发生一个粗推迟的脉冲信号,完结以10 ns为步进的推迟,推迟分辨率为10 ns级。FPGA内部结构如图2所示。

图2 FPGA内部结构框图

FPGA将粗推迟脉冲信号送给多路推迟线芯片DS1020进行低位推迟。实践电路中DS1020的8个并行数据引脚(P0~P7)与MCU相连,MCU通过软件程序将推迟时刻写入DS1020,并发送指令给EN端口,告诉DS1020完结低位延时。通过与MCU相连的8位数据脚完结10 ns以内的延时,最终输出脚OUTPUT将脉冲信号送至D/A转换器,再经扩大器扩大后得到总推迟后的输出信号。多路推迟线结构框图如图3所示。

图3 多路推迟线结构框图

4 体系仿真

下面给出了中心部分的RTL图及QuartusII时序仿真波形。PLL模块的RTL图如图4所示。

计数模块2的RTL图如图5所示。该模块的输入clk应衔接到频率为100 MHz的时钟信号,作为计数脉冲。 en是使能信号, 应衔接到通过计数模块1分频后得到的1 kHz的时钟信号上。假定en信号到来,该信号为高电平时,计数器temp开端计数,抵达设定的计数时刻后输出高电平,否则为低电平。通过计数模块2后体系完结粗推迟,此刻推迟分辨率为10 ns级。

图4 PLL模块RTL图

图5 计数模块2的RTL图

PLL模块完结倍频的功用。其间,输入clk0应衔接频率为50 MHz的时钟信号。输出信号c0为100 MHz,别离送给计数模块1和2完结分频和计数脉冲的效果。其仿真波形如图6所示。

图6 PLL模块仿真波形

计数模块1和2的推迟时刻均可由单片机动态写入,本政策波形写入的推迟时刻为300 ns。推迟后的波形如图7所示。

结语

本规划不同于现有的推迟电路,它将数字办法图7推迟后计数模块2输出波形和模仿办法相结合,对多路接连脉冲信号进行大规模高分辨率的动态推迟,将分辨率进步到了0.15 ns级。并且,本体系用Flash FPGA代替现有体系的SRAM FPGA,然后大大进步了体系集成度,降低了本钱。

责任编辑:gt