FPGA面世现已超越20年,现在FPGA在杂乱逻辑电路以及数字信号处理范畴中扮演着越来越重要的人物,SoC以其低功耗、高功用、低成本、高可靠性等长处成为嵌入式体系的发展趋势。不过,关于许多规划者来讲这仍是“新鲜事物”。学习并把握一项新的技能或具有某种才能,比方学习FPGA开发技能并将其运用到实践体系中,这是一项艰巨使命。Altium Designer 供给了一种简略轻松的办法,能够协助软/硬件工程师一同应对FPGA嵌入式体系开发的应战。Altium designer具有强壮的嵌入式体系规划功用以及十分方便的规划流程,它在FPGA 及嵌入式智能方面有如下优势:

1) 完好功用、一致的规划环境

a) 简略易用的FPGA规划东西链(包含原理图和HDL言语混合修改器、编译器、归纳器和下载)

b) 完好的嵌入式软件开发环境(包含修改器、编译器、生成器、联接器和调试器)

c) 立异性体系验证渠道——NB2 (搭载了丰厚的外围接口板和可彼此替换的FPGA子板)

2) 数字组合逻辑电路开发功用

a) 放置和联接预先归纳的器材

b) 电路原理图和 HDL言语混合输入办法

c) 丰厚的虚拟仪器模块

d) 高度抽象化的体系规划——OpenBus

e) 灵敏的C言语到HDL言语转化——CtoH

3) 嵌入式软件规划功用

a) 专业的编码环境

b) 独立于处理器的 Viper C-编译器

c) 方针代码自在的移植——DSF

d) 完好的源代码级调试

4) 立异性体系验证渠道NB2(施行并调试你的计划)

a) 独立于FPGA厂商的子板

b) 灵敏的外围设备板

c) 实时调试和更新

d) 对产品板的继续研制

5) 规划施行形式间紧密结合

a) 规划移动到方针硬件

b) PCB和FPGA间规划协同

接下来,咱们将在AlTIum Designer渠道下,运用一个视频捕获输出的实例去亲自体会怎么轻松、方便地完结FPGA嵌入式体系规划。在这个比如中,咱们将运用AlTIum Designer内的几个专门针对进步规划功率,简洁规划进程而开发的特定功用。它们包含:OpenBus体系开发;FPGA项目的主动装备;处理器软件架构——DSF。

别的,本例中还将结合NB2的板级硬件资源,加速计划验证和施行的进程;

* 复合视频码流输入模块(Composite video capture)

* 接触TFT显示屏模块(Touchscreen TFT display)

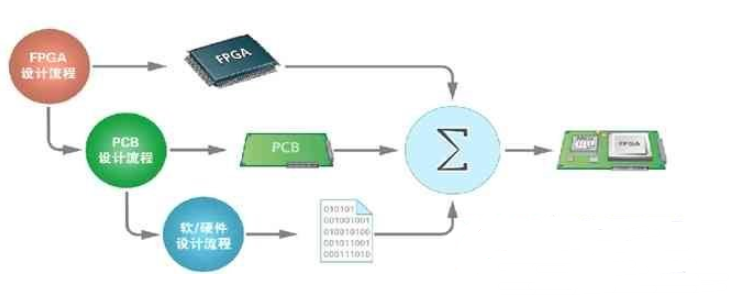

图1是体系架构示意图,该体系可运用于根据视频捕获和信号处理等规划范畴。

图1 体系计划示意图。

传统的体系规划流程

传统上,应对包含FPGA器材规划和嵌入式软件规划的体系开发流程需求阅历三个阶段(图2)。

图2 传统的体系规划流程

1、 FPGA规划;

2、 PCB规划;

3、 嵌入式软件规划

每个阶段彼此联接,逐次完结;因为需求在规划初期完结元器材选型(包含FPGA器材和微处理器),因此必将下降全体计划完结的灵敏性;关于规划后期或许在器材功用及功用扩展等方面呈现的问题,需求消耗规划者更多的精力才或许补偿,或许只能将现有计划推倒重来。

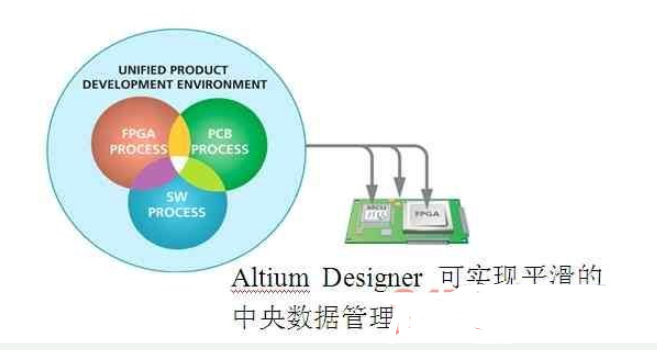

图3、 立异的体系规划流程。

立异性的体系规划流程

运用AlTIum Designer渠道完结FPGA的嵌入式体系规划,首要要为体系计划创立一个FPGA工程,并在工程内增加源规划文档。

在数字组合逻辑电路规划输入方面,一个FPGA项目支撑三种类型的输入办法-原理图、HDL (Verilog 或VHDL)以及OpenBus。别的还支撑C代码符号的输入。你能够运用这些输入办法的混合输入,并运用层次原理图所用到的符号方块图来对不同的输入文档进行组合。关于FPGA项目,必须将原理图做为顶层文档,因为这是为了支撑从FPGA到PCB移植以及同步。首要,创立一个原理图文档并增加到项目中去。如图4所示。

图4 FPGA项目以及新生成的文档的项目面板

接下来,咱们一同体会OpenBus体系规划简易、方便的特性。OpenBus是一个进行体系级 FPGA规划的新办法。它供给了比原理图更为简略的界面,可是并不会因其简略而丢掉相应的信息。因为它能主动考虑底层细节,因此规划者只需着眼于顶层体系的规划以及首要元件的互连。而这些元件都是预先归纳过的、运用于FPGA开发的IP元件。

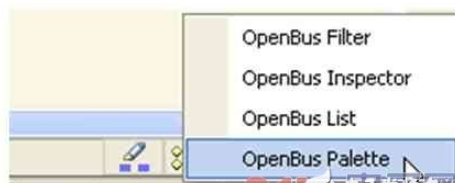

图5 OpenBus面板

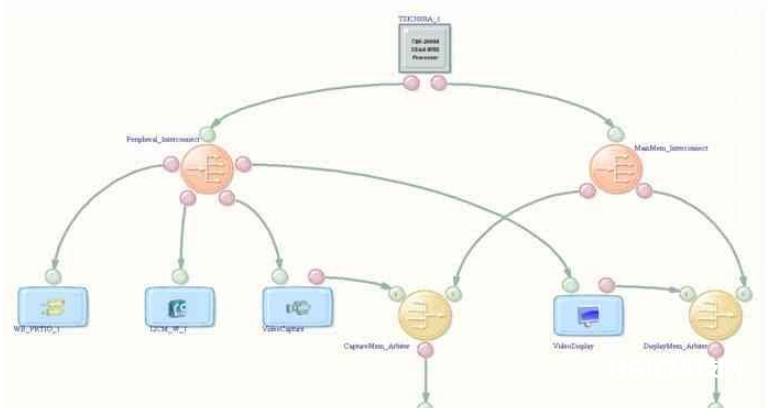

在AlTIum Designer渠道中OpenBus文件修改环境下(如图5所示),你将开端亲自体会怎么轻松、方便地完结FPGA的嵌入式体系规划。如图6所示,全体计划的完结与咱们对计划规划规划时,描绘的体系结构结构十分类似。根据完结计划所需用到的功用单元,比如:32位微处理器、视频输入操控模块、TFT显示屏操控模块、I2C操控模块(用于操作视频流数据输入处理器材的操控寄存器单元)、IP内核互连模块、SRAM操控模块和总线裁定模块,从OpenBus器材列表栏中逐个放置到当时修改文档内,并完结联接。

图6 完结的OpenBus规划

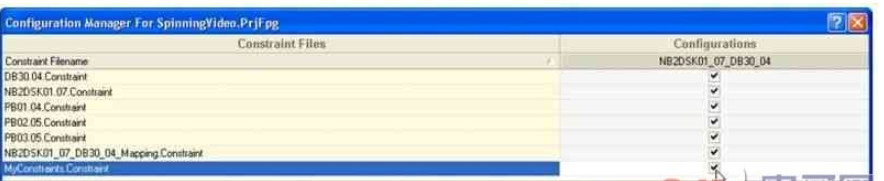

随后,还需求为包含SRAM操控器、总线裁定器、IP内核互连器和微处理器等OpenBus元件装备运用参数。Altium Designer支撑独立于FPGA器材原厂商的规划。也就是说,你能够从头绑定你的规划到别的一个厂商的别的一块FPGA芯片。这种移植进程能够经过 Altium Designer的装备管理器(configuration management)容易完结。如图7所示,不同的装备文件以及束缚文件能够从头绑定规划到不同的FPGA芯片。

图7 增加束缚文件到装备管理器

至此,你现已为你的嵌入式体系规划计划建立好了完好的运用渠道。终究,你还需求为体系增加嵌入式智能操控软件,终究完结FPGA的嵌入式体系规划。 Altium Designer渠道下的嵌入式软件开发功用将帮你轻松应对软件规划中所遇到的任何应战;一个嵌入式项目能够独登时进行开发,可是终究需求这些代码在方针处理器中运转。Altium Designer给你简洁的办法,将你的嵌入式项目联接到包含有嵌入式处理器核的FPGA项目中去。

本实例中的处理器核即为OpenBus文档顶用的32位处理器核TSK3000A_1。左键点击并拖动嵌入式项目到上面的FPGA项目。并将嵌入式项目丢在TSK3000A_1 处理器核上(FPGA项目中的处理器核会主动高亮)。如图8所示。在你联接好这两个项目之后,一个新的C头文件会主动增加到嵌入式项目中去。这个头文件 hardware.h由FPGA项目编译的时分主动发生。当完结了嵌入式软件代码的开发后,你就能够在NB2渠道下,实时现场调试和验证你的规划计划。正如本篇开端的体系结构示意图所示,你能够将摄像头所捕获的视频信号呈现在TFT显示屏上。

图8 链接嵌入式项目到处理器核

假如你还想增强体系处理视频码流的功用,使得视频图片能够在TFT显示屏上快速缩放以及旋转,那么需求用到Altium Designer的C-to-hardware转化功用CHC。别的在上述的OpenBus文件里需求运用特别运用处理器 ASP元件。因为运用了C-to-hardware功用,你能够决议哪些C代码函数需求用数字组合逻辑功用完结,哪些用微处理器完结。因为采用了硬件来完结矢量图形的缩放功用,因此相关于软件完结将愈加速速。这方面能够在本实例中进行实验验证。

在FPGA规划完结之后,Altium Designer还供给一个方便的办法,可将FPGA项目直接转化到相应的PCB项目,并进行项目之间数据的同步更新。总归,Altium Designer在FPGA以及SOPC方面供给了强壮且方便好用的功用,包含一致、完好的规划环境;多种规划输入方法;独立于处理器的灵敏代码;C- to-hardware;可重构的验证渠道;独立于FPGA原厂商的规划;规划仿真;虚拟仪器及LiveDesign交互式调试,以及方便方便的FPGA 项目到PCB项目数据同步功用。这些强壮的软件功用连同可重构的体系验证渠道NB2一同为你供给了一个功用强壮的立异渠道,在这个立异渠道上,规划者能够纵情放飞规划创意,来发明更有价值的规划。