导言

现在FPGA经过USB接口获取USB设备中数据的计划大致分为两大类,一类为在FPGA内部完结USB设备操控,另一类为在FPGA外部完结USB设备操控。在FPGA内部完结的计划需求在FPGA内部完结USB操控器,在内部完结或许外接USB收发器。该计划的完结具有较大难度,一起由于USB协议和文件体系都适当杂乱,需求运用适当多的FPGA资源,因而彻底不能满意快速开发和低FPGA资源占用率的要求。在FPGA外部完结的计划一般运用单芯片的USB解决计划,典型的计划有两种:一种是集成了USB操控器和USB收发器,但需自行完结文件体系,如美国Cypress公司的CY7C67300;另一种是完结了包含文件体系在内的一切USB读取U盘所需的软硬件,只需求FPGA发送指令进行操控即可完结读取U盘,如南京沁恒电子的CH376。在这两类计划中,CY7C67300集成度高,但其只支撑USB 1.1,传输速率较低;一起需求FPGA对其进行装备和操控及完结文件体系,FPGA端的开发量较大。CH376支撑USB2.0接口,是一个真实的单芯片解决计划;但CH376只支撑FAT16/32文件体系,不支撑NTFS文件体系,无法读取大于4 GB的大文件。别的,CH376需求FPGA进行装备和操控,因而需求完结CH376的操控逻辑并占用必定的FPGA资源。

由于现有计划均存在数据传输速率低、FPGA开发量大的缺陷,本文提出了一种运用ARM+FPGA的计划,经过ARM处理器读取USB设备数据并传输给FPGA,然后完结FPGA从USB设备获取数据。该计划既能到达较高的数据传输速率,又能下降FPGA开发量,一起还具有很高的灵活性。

1 体系规划

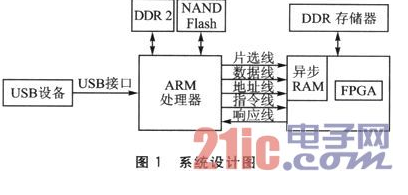

本计划的体系规划如图1所示。该体系由ARM处理器、FPGA和USB设备构成,FPGA经过内部拓荒的异步RAM空间接纳数据,ARM处理器担任将USB设备中数据经过并行总线转发给FPGA,USB设备支撑常见的U盘、照相机、移动硬盘等支撑USB接口的从设备。本规划还将ARM处理器的两个引脚与FPGA的通讯。指令线用于ARM向FPGA发送预备进行数据传输的指令;呼应线用于FPGA在接纳到ARM的告诉并预备好后呼应ARM。与FPGA相连的DDR存储器用于高速缓存很多图画数据,支撑常见的DDR、DDR2和DDR3等类型。

1.1 ARM处理器挑选

本计划选用的ARM处理器为韩国三星公司的S5PV210。S5PV210是一款依据ARM Cortex—A8内核的RSIC处理器,该芯片具有强壮的核算才能、丰厚的内部资源和外部接口,主频高达1 GHz,一起它还具有优化的外部存储器接口。外部存储器接口为异步接口,时钟频率为133MHz,位宽为16位,具有完善且可调的时序操控功用,可用于衔接ROM、SRAM、oneNAND、NAND Flash等多种存储器,能满意在高端通讯服务中的数据带宽要求。本计划运用这个接口完结数据从ARM处理器到FPGA的高速传输。

1.2 ARM与FPGA接口规划

本计划将FPGA异步RAM衔接在ARM处理器的XM0内存总线上,作为一个位宽为16位的SRAM运用,其对应的硬件地址为0x10000000到0x1000 1002,共4 098字节。由于异步RAM的位宽为16位,故只需运用地址线ADDR 1~ADDR 13。指令线衔接ARM处理器的GPIO引脚,方向为输出,高电平有用。呼应线衔接ARM处理器的中止引脚,方向为输入,上升沿有用。

1.3 软件规划

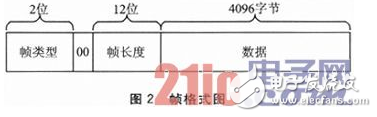

在本计划中,ARM处理器以帧为单位向FPGA传输数据。每帧长度为4 098字节,其间,帧头长度为2字节,数据长度为4 096字节。帧格局如图2所示。

帧类型的取值为:此帧不是最终帧为00,此帧是最终帧则为11。帧长度为帧数据的长度,以字节为单位。

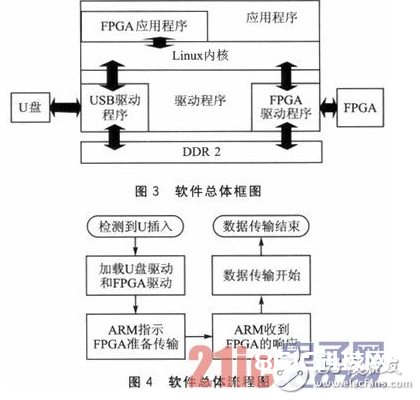

本计划所规划的软件分为两个部分逐个驱动程序和运用程序,软件整体框图如图3所示。驱动程序在Linux体系中注册硬件并供给操控硬件的功用函数,以供运用程序调用。运用程序运用驱动程序供给的功用函数操控硬件,完结整个传输进程。软件整体流程图如图4所示。

1.3.1 驱动程序规划

本计划触及3种驱动程序:USB驱动程序、文件体系驱动程序和FPGA驱动程序。

Linux体系有丰厚完善的USB设备和文件体系支撑。本计划运用Linux体系中自带的USB Mass Storage驱动程序和文件体系驱动程序,自行编写FPGA驱动程序。FPGA驱动程序依据Linux体系字符设备驱动程序模型进行编写。FPGA驱动程序的首要函数有初始化函数init()、写入中止服务函数write_int()、写入函数write()。

初始化函数init()首要将FPGA异步RAM对应的硬件地址0x10000000~0x10001002映射为Linux体系中的内存虚拟地址A到A+4098(设映射的内存虚拟地址开端为A),完结在Linux体系中直接向异步RAM写入数据。然后,设置指令线、呼应线所对应的寄存器。将指令线的方向设置为输出,并输出低电平;呼应线的方向设置为中止输入。最终,函数将呼应线中止服务函数设置为write_int()。

写入函数write()与写入中止服务函数write_int()合作,完结一次数据传输:

①当运用程序调用写入函数后,函数首要设置指令线为高电平指示FPGA预备传输数据,然后将驱动程序置于休眠状况,等候唤醒。

②FPGA收到指令后判别现在能否传输数据,如果能,则在中止线上发送一个上升沿。ARM处理器捕捉到该上升沿后,调用write_int(),唤醒驱动程序。

③驱动程序被唤醒后,持续履行write()。write()函数首要依据运用程序供给的参数生成帧头,并将帧头写入地址ADDR和ADDR+1,完结帧头的传输。随后将数据写入地址ADDR+2及这以后的地址,完结数据的传输。

1.3.2 运用程序规划

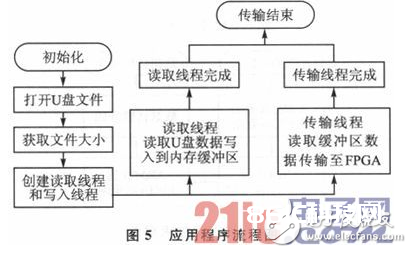

本计划经过Linux体系的热插拔机制主动发动运用程序。在U盘刺进USB接口后,Linux体系主动加载USB驱动和FPGA驱动并发动运用程序。运用程序流程如图5所示。

运转运用程序时,经过设置参数能使运用程序读取U盘、移动硬盘乃至网络上的文件,使计划具有很高的灵活性。运用程序运用了多线程技能来充分利用体系资源,运用两个线程别离完结从U盘读取数据存入缓冲区的进程和将缓冲区内的数据传输至FPGA的进程。在读取线程或写入线程中,能够参加数据处理代码完结数据的预处理,削减FPGA工作量。运用程序分配了多个缓冲区进步功能,并运用了互斥锁完结读取线程与传输线程间的线程同步,保证数据正确传输。

1.4 ARM向FPGA传输数据规划

本计划在FPGA中完结一个异步RAM,其运用乒乓机制接纳来自ARM处理器的数据,一起需求将异步RAM中的数据写入DDR 2存储器。异步RAM内部有两个数据缓冲模块。在乒乓机制中,两个模块别离履行不同的使命,当模块1接纳数据来自ARM处理器的数据时,模块2将数据写入DDR 2存储器。当两个模块的使命都完结后,交流模块1和模块2的使命。与现有计划比较,本计划FPGA无需装备外部芯片,所需开发量较小。

2 测验与剖析

2.1 传输速率测验

此测验传输3个不同巨细的文件,记载数据传输时刻,然后取得数据传输速率。

测验成果如表1所列。

由表1可知,在传输速率测验中,测得的最高数据传输速率为47.6 Mbps,比现有计划如CY7C67300、CH376的数据传输速率高。在传输速率测验中,传输100 KB文件的传输速率与传输1 MB和1 GB文件的传输速率比较偏低,而传输1 MB和1 GB文件的传输速率则相差不大。原由于:

①测验为先进行计时后开端传输,存在一段时刻未传输数据。

②运用程序在传输开端前需求一段时刻进行初始化,存在一段时刻未传输数据。

在后两种测验中,以上两种未传输数据的时刻占总时刻的比重较低,因而数据传输速率较高。

2.2 传输准确率测验

此测验在FPGA内完结一个比较器,比较异步RAM接纳到的数据与比较器内置数据是否共同,然后测验传输是否正确并确认正确率。经测验,此计划在传输进程中无差错产生,传输正确率为100%。

结语

FPGA与ARM处理器相合作完结FPGA高速获取U盘数据的计划,能够满意FPGA高速读取U盘数据的需求。在传输进程中无差错,且具有杰出的灵活性。本计划具有很高的实用价值。