Jan Gray是在FPGA中集成32位RISC处理器的专家,他写了一篇博客叫作FPGA CPU 新闻,副标题为 “运用FPGA开发并行计算机系统架构”。 Jan Gray的最新帖子为FPGAs, 其时和现在,这篇帖子将1995年在Xilinx XC4010PC84-5 FPGA中集成J32 32-bit RISC CPU与现在XilinxVirtex-7XC7VX690T FPGA 集成同一处理器进行了比照。Gray 运用的J32处理器选用经典RISC架构,带有3-operand操作指令,4=stage流水线(提取、寄存器读、履行、回写),和32位操作数寄存器文件。

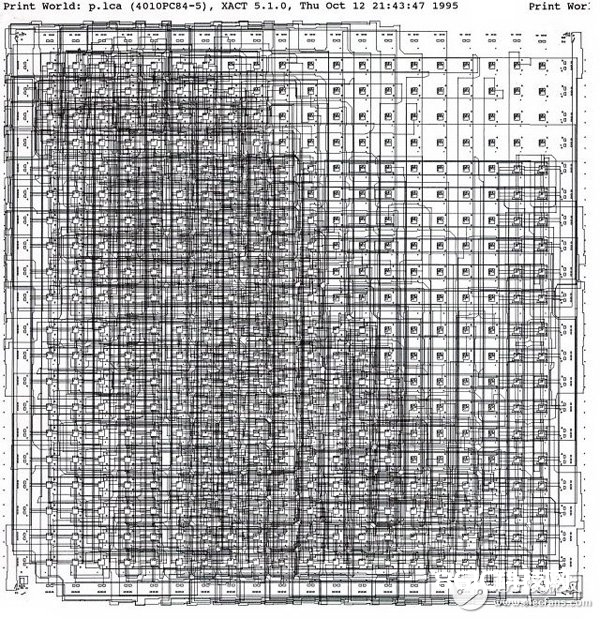

1995年,Gray运用的J32处理器根本耗费了XC4010 FPGA中800个4-input LUT。处理器摆放看起来是这样:

13年今后。同一J32处理器内核集成在Virtex – 7 FPGA,它支撑433,000以上的6输入 LUT,是250个路由器中心与1000个处理器互连预留空间的1000倍。J32 RISC处理器的摆放看起来像这样:

“也就是说曩昔18年摩尔定律将每个FPGA集成1K LUT晋级至每个FPGA集成1K 32-bit CPU。(趁便说下,规划最大的Virtex Ultrascale 3D FPGA有440万个逻辑单元,所以逻辑容量满足10,000个以上Jan Gray所说到的 32位RISC J32 CPU进行互连。且看以下的注释阐明!)