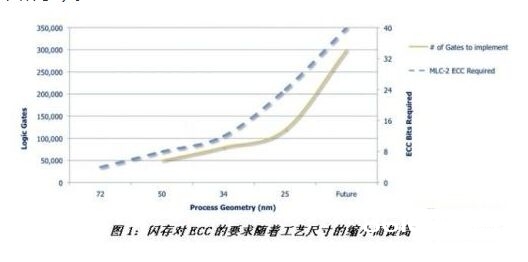

自面世以来,NAND闪存对ECC(纠错码)纠错才干的要求越来越高。尽管这不是一个新问题,可是支撑最新的多层单元(MLC)架构和每单元存储三位数据(three-bit-per-cell)技能所需的ECC纠错才干让体系人员越来越难以敷衍。

曩昔,ECC一向被用于进步NAND闪存子体系的全体数据可靠性。可是,跟着NAND单元不断缩小,每个浮栅内储存的电子数量越来越少。因而,为补偿更小的存储单元所发生的更高的位误码率,咱们有必要大幅进步ECC纠错才干,以坚持所需的体系可靠性。

跟着体系对ECC纠错要求不断进步,完结ECC逻辑所需的逻辑门数量也在添加,一同体系复杂性也随之进步。例如,24位ECC需求大约200,000个逻辑门,而40位ECC则需求大约300,000个逻辑门。据估计,将来先进的ECC算法或许需求近100万个逻辑门(如图1所示)。

许多高功用闪存体系有必要运用多通道NAND闪存才干完结抱负的功用。在这些体系中,每个通道都有其自己的ECC逻辑。例如,一个10通道固态硬盘(SSD)需求完结10通道的ECC逻辑。假定10路通道中的每一路通道都需求60位ECC,那么仅ECC逻辑就需求300万个逻辑门。

NAND闪存接口挑选

1.传统NAND接口

传统的NAND闪存接口是一种异步通讯接口,尽管近几年这种接口的速度已进步到50MHz,可是其它特性并没有太大的改变。

几年前,美光(Micron)与其它几家赋有远见的公司一同成立了一家NAND闪存安排,旨在简化业界存在的许多时序和指令规范。开放式NAND闪存接口(ONFI)联盟发布了其第一版ONFI 1.0规范,与开始的规范比较,这个接口规范的最大特点是主处理器能够经过电子方法辨认所衔接的闪存类型,以及其它重要的技能参数,如时序形式、页面巨细、块巨细、ECC要求等。该特性被一切的ONFI规范承继下来,而且一向是一切ONFI规范的重要内容。

同步NAND接口的开发是ONFI联盟获得的另一个重要成果,这一接口规范又称为ONFI 2。现在,ONFI 2.2规范经过一个DDR源同步接口支撑高达每秒20000万次传输(200MT/s)。通电后该接口可用于异步通讯形式。可是,关于更高的功用而言,当从异步形式转换到同步通讯形式时,主处理器会提早问询闪存设备是否支撑更高速的同步通讯接口。

2.Direct NAND解决计划

该计划完结经过将NAND闪存芯片直接衔接到主处理器或SSD操控器来办理NAND闪存。ECC算法交由硬件处理,而软件一般履行一切的区块办理和损耗均衡功用。初看起来该计划或许并不抱负,但考虑到今日的嵌入式处理器典型运转速度到达数百兆赫兹,许多乃至超越千兆赫兹,这些高功用处理器能够以更快的速度履行区块办理,并运用承认性多线程技能来进步闪存功用。此外,由于主处理器直接办理闪存设备,主处理器软件能够做出实时决议,这有助于防止因意外断电而形成的危险。

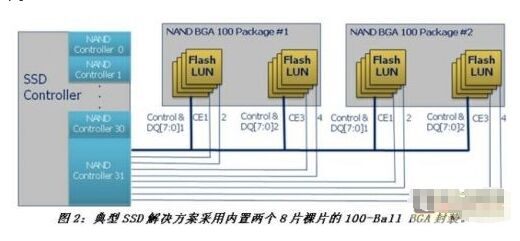

如图2所示,ONFI 2.2接口规范(200MT/s)最多可支撑16个规范NAND闪存芯片,典型解决计划一般选用两个8片NAND闪存封装。规范8片100-BallBGA封装含有两条独立的NAND总线(DQ[7:0]1和DQ[7:0]2),每条总线衔接4片NAND闪存。闪存操控器经过两个芯片使能信号操控每四片堆叠的裸片。典型规划是把两条数据总线即DQ总线衔接到一同,为每个封装供给一条8位数据总线。最高装备由两个内置8片裸片的100-Ball BGA封装组成。为选定一个特定的NAND裸片,每个规范100-Ball BGA封装需求供给四个芯片使能(CE#)操控。因而,为支撑这种装备,主处理器或SSD操控器需求供给8个芯片使能信号。

3.ClearNAND解决计划

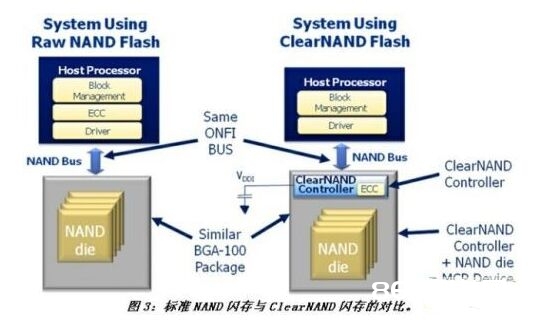

图3显现了两个不同的体系完结:传统的体系中主处理器或SSD操控器与NAND闪存直接相连;另一个体系则选用ClearNAND闪存芯片。两种计划都选用相同的ONFI硬件接口和类似的100-Ball BGA封装,不同之处是后者将一个薄型操控器与NAND闪存裸片整合在一个多芯片封装(MCP)内。ClearNAND 操控器用于完结MCP封装中NAND闪存所需的ECC算法。由于选用相同的ONFI异步或同步接口,规划人员能够轻松地从规范NAND闪存晋级到 ClearNAND闪存。

美光公司的ClearNAND 闪存分为规范型和增强型两个版别。规范型ClearNAND闪存首要用于消费电子设备,可完结所需的ECC功用,并供给便于闪存晋级的传统异步型ONFI总线。

增强型ClearNAND闪存能够办理ECC算法,并供给多个关于企业运用颇具价值的要害功用。它还支撑ONFI 2.2接口的异步和同步通讯规范,可用存储容量高达64GB。

经过改进ECC算法,两款ClearNAND闪存都能够完结下一代NAND闪存所需的ECC纠错功用。这使得规划人员无需重复从头规划电路来支撑制造商最新的NAND ECC要求。

增强型ClearNAND闪存

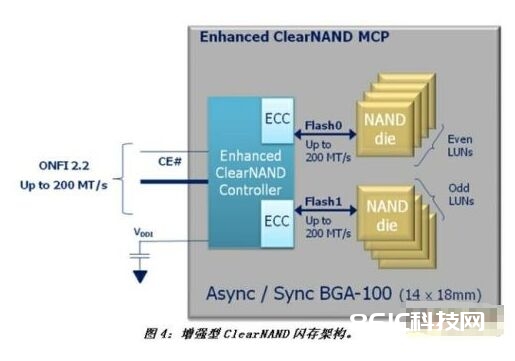

图4所示为增强型ClearNAND闪存的架构。它支撑1个ONFI 2.2接口和速度高达200MT/s的指令、地址和数据总线。VDDI去耦%&&&&&%常见于e?MMC产品和内含操控器的其它闪存,用于对内部稳压器进行去耦。为向后兼容传统NAND闪存,VDDI衔接放置在一个搁置引脚上。ClearNAND操控器支撑两条内部闪存总线,其间一条用于衔接偶数编号的逻辑单元(LUN),另一条则衔接奇数编号的逻辑单元。这两条独立闪存总线的速度高达200MT/s。此外,每条总线都配有各自的ECC引擎,可在两条总线上一同办理读操作或写操作。能够预见,未来的操控器还将支撑面向400MT/s的ONFI 3接口规范。

下面将评论增强型ClearNAND供给的四项高档功用:卷寻址、电子数据映像、中止功用和内部回写(copyback)。

卷寻址

卷寻址答应一个片选或芯片发动信号(CE#)对16个ClearNAND卷进行寻址。每个 ClearNAND操控器支撑在一个MCP封装内堆叠8个裸片。ClearNAND操控器为主处理器或SSD操控器存取操作供给一个缓冲区。

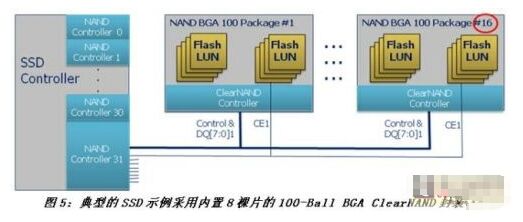

如图5所示,增强型ClearNAND规划将存储容量扩展八倍,一同坚持或进步了信号完整性,并减少了所需的有用芯片使能数量。这是由于关于SSD操控器,一个ClearNAND操控器仅代表一个负载,可是在一个MCP封装内最多可支撑八个NAND裸片。

卷寻址概念有两层意义。第一层是为每个ClearNAND 封装承认卷地址。卷地址仅在初始化时分配一次,并保存到电源重启停止。第二层意义是卷挑选指令自身,在这个新指令后边紧跟一个单字节(实际上只需4位)卷地址。一旦方针地址被挑选,该地址就会坚持被选状况,直到另一个卷被挑选停止。这能够节约许多使能引脚。例如,一个32通道SSD需求8个使能引脚来操控两个8裸片规范NAND封装。上述32通道SSD示例需求一共256个使能引脚,而增强型ClearNAND卷寻址功用对相同数量的NAND闪存进行寻址只需32个使能引脚。此外,这相同的32个使能引脚可寻址容量是现有容量的八倍。

电子数据映像

增强型ClearNAND支撑电子数据映像,这答应经过电子方法将数据总线信号次序重映射为两种装备之一。这个功用关于PCB正反两面都装置ClearNAND闪存的高密度规划十分有用。运用一个特别的初始化或复位序列,ClearNAND封装能够以电子方法检测闪存是装置在PCB的正面仍是反面。例如,一般的做法是在上电后向闪存发送一个复位或FFh指令。为完结电子DQ映像,在履行完FFh指令后,主处理器有必要接着履行传统的READ STATUS(70h)指令。装置在PCB正面的闪存检测到FFh-70h指令序列;而装置在PCB反面的闪存则检测到FFh-0Eh指令序列,并向主处理器承认这是反面闪存封装,然后从头将数据总线直接排在正面闪存的后边,这不仅能够改进PCB的布线,还能进步信号完整性。

Ready/Busy#被从头界说为中止

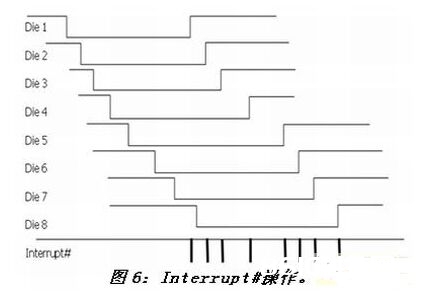

增强型ClearNAND闪存将现有的ready/busy#引脚从头界说为一个中止引脚。如图6所示,interrupt#信号仍是开漏信号,当ClearNAND卷或裸片安排妥当时,它供给一个实时中止信号。规划人员能够运用这个中止信号向主处理器或SSD操控器供给闪存实时状况。在一条总线上支撑多个ClearNAND封装的大型装备中,interrupt#信号线能够衔接在一同。当检测到一个中止信号时,主处理器或SSD操控器只需问询每个ClearNAND 封装或卷,即可知道是哪个卷发送的新状况信息。这个中止功用可节约主处理器或SSD操控器上的信号数量,一同进步SSD操控器对状况更新的呼应才干。

内部回写

内部回写功用又称为内部数据搬迁(internal data move),是增强型ClearNAND 闪存最有目共睹的特性之一。闪存的损耗均衡或碎片收拾操作是指收拾不同的NAND闪存页面和区块内的数据碎片,并将其合并成新的区块或区块序列,这个功用类似旧式硬盘的磁盘碎片收拾东西。关于这类操作,回写功用可为SSD体系供给巨大的优势。

再来看图2,当运用规范NAND闪存时,将数据碎片从一个区块转移到另一个区块一般需求履行下列操作:

SSD操控器发布一个READ指令和源地址以拜访数据源页;SSD操控器从NAND闪存读取数据,一同履行运算和必要的ECC纠错操作,然后完结数据或元数据的更新操作;SSD操控器核算并参加新的ECC信息,然后发布新的PROGRAM指令、意图地址和数据序列,该操作将把数据保存到新的NAND闪存区块内。

在这个接连的操作过程中,当数据从源地址移到意图地址时,总线处于被占用状况,这个操作过程需求很长时刻。假定一个8K的存储页,作业在200MT/s的ONFI 2.2同步总线需求大约 41μs来移动数据。由于数据有必要移出再移进闪存,所以需求两倍的时刻即82μs,但这个时刻不包括ECC所花费的时刻。在履行这个序列的过程中,ONFI闪存总线一直处于占用状况,不能处理其它任何操作。

与一般闪存不同,增强型ClearNAND闪存支撑内部ECC。假定数据的源地址和意图地址都在ClearNAND封装内,选用内部ECC能够在封装内部履行回写操作。SSD操控器仍担任发布指令和地址,以及经修正的数据或元数据。ClearNAND操控器履行数据搬迁操作,而不会占用外部的ONFI数据总线。假如SSD操控器能够把损耗均衡和碎片收拾功用整合在一个ClearNAND封装内,它将在功用方面具有更强的优势。

图7所示是一个在标识为通道0和通道1的两路ONFI通道上选用增强型ClearNAND闪存的示例。在两个SSD通道上,咱们看到有四个内部数据搬迁操作同步进行,数据移动并没有占用外部ONFI总线。在必要时,这个特性答应SSD操控器和ONFI总线在ClearNAND封装之间搬迁数据。依据用户所运用的架构,某些操作或许需求在ClearNAND封装之间乃至ONFI总线之间进行。运用内部数据搬迁操作,可大幅进步碎片收拾和损耗均衡操作的功用。

本文小结

美光公司的增强型ClearNAND闪存为体系规划人员供给更高的功用和更多的功用,一同缓解了NAND闪存对ECC纠错才干的日益严厉的要求。增强型ClearNAND闪存支撑与规范100-Ball BGA NAND闪存类似的焊球摆放,用户能够规划出一同支撑这两种封装的产品。例如,该产品将使SSD主操控器具有足够的ECC纠错才干来直接支撑SLC NAND闪存,挑选增强型ClearNAND闪存还能满意ECC面对更大应战的多级单元需求。

增强型ClearNAND闪存的卷寻址特性可运用更少的引脚完结更大容量寻址,然后为SSD计划中节约数百个引脚。电子数据映像功用可简化PCB规划和走线,一同还能进步ONFI总线的信号完整性。智能中止功用向SSD操控器供给实时状况更新信息,并最大极限地缩小对固件的轮询。两路内部NAND闪存总线可改进回写功用,然后进步闪存的功用。