逻辑剖析仪是一种通用数据域测验仪器。使用在由中大规模数字集成电路组成的数字体系中,首要查找总线相关性毛病,能以多种办法盯梢与显现总线上的数据流,是丈量范畴不行短少的东西。

跟着电子技术和核算机技术的开展,逻辑剖析仪与 PC机相结合,研制的虚拟逻辑剖析仪是近年的一个新的开展方向,两者的结合扩展了逻辑剖析仪的剖析和核算才能,提高了性价比,且增强了仪器的通用性。现场可编程逻辑器材FPGA,是一种可由用户依据所规划的数字体系的要求,在现场由自己装备、界说的高密度专用数字集成电路。它具有规划便利、灵敏、校验快和规划可重复改动的特色。

本文提出了一种依据FPGA的虚拟逻辑剖析仪的规划办法。该体系对收集到的模仿或数字信号进行存储、预处理和逻辑剖析。经过FPGA操控数据单次或接连收集、缓冲,经过PCI9030将缓冲区数据转移到硬盘办理卡,由硬盘办理卡将数据存入海量硬盘。

1 体系结构规划

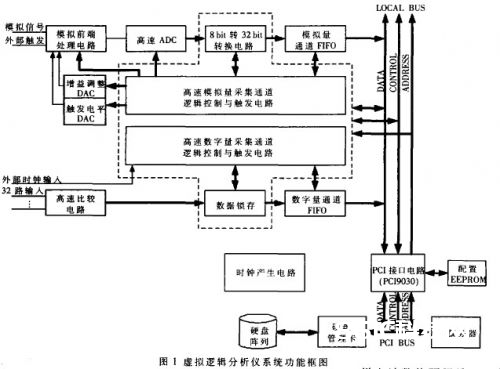

本文规划的虚拟逻辑剖析仪首要由高速模仿量收集通道、高速数字量收集通道、PCI接口电路、时钟发生电路四部分组成。数据收集体系要处理的问题首要是数据的收集和传输问题。为了增强规划的灵敏性和可扩展性,体系选用FPGA(Field Programmable Logic Array)来完结对A/D转化器、数据缓冲器、时钟、数据传输的逻辑操控。体系功用框图如图1所示。

2 FPGA在体系中的使用

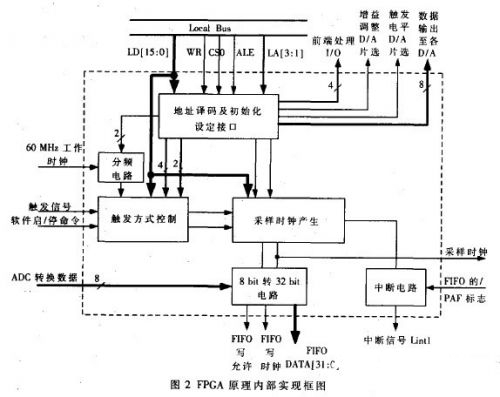

FPGA范畴的快速开展使FPGA片上资源许多丰厚,尤其是其高速功用和片上RAM使其特别适用于高速数据收集体系的规划。规划选用Altera公司的FLEX10K30E,该器材含有8个EAB(嵌入式阵列),每个EAB能够供给4 Kbit存储位,每个EAB都有双口RAM完结才能;供给30 000逻辑门;支撑PCI总线,可供给 66 MHz的PCI功用;门级延时仅为6.5 ns。本体系中FPGA规划首要包含地址译码及初始化接口电路、分频电路、触发办法操控电路、采样时钟发生电路、8 bit转32 bit电路、中止电路等。FPGA功用框图如图2所示。

3 体系功用剖析与体系描绘

依据前面评论的体系级规划办法,首要对高速模仿量收集通道逻辑操控与触发电路所应具有的功用进行剖析。概括出本部分电路应完结的功用首要有以下几点:(1)软件初始化设定的接口;(2)触发办法操控;(3)采样时钟发生;(4)发动/中止采样及数据的缓存与读取。

3.1 软件初始化设定

收集通道的初始化设定首要包含耦合办法挑选、前端电路使能、触发源(内/外触发)挑选、触发办法设定、采样办法及采样频率设定。这些设定均选用模仿量收集通道作业办法寄存器(16 bit)的各标志位来操控。作业办法寄存器作为Local Bus的I/O端口来操作。别的,还有触发推迟计数值预置端口、触发超前计数值预置端口、采样点计数值预置端口、增益调整D/A转化操作端口以及触发电平D/A转化操作端口等I/O端口。这些I/O端口组成一个接连的I/O地址规模,由Local Bus总线译码来寻址并进行相应I/O操作。

3.2 触发办法操控

本规划供给了三种常用的触发办法:当即电平触发、推迟电平触发、超前电平触发。依据外部触发信号挑选所需的触发办法。

3.3 采样时钟

因为受高速ADC最低采样频率的约束(最低为5 MHz,低于此值会形成ADC的量化差错急剧增大,乃至ADC不能正常作业),因而,本文规划的异步采样供给了四种采样频率:由60 MHz有源晶振供给基准时钟送到FPGA的可编程分频器,经过可编程分频电路之后发生60 MHz、30 MHz、15 MHz、7.5 MHz四种时钟输出到触发办法操控器中。把时钟信号和触发办法送到采样时钟发生电路中发生体系需求的各个时钟信号。

3.4发动/中止采样及数据的缓存与读取

由核算机软件宣布发动指令后开端采样,并同步将ADC输出的8 bit数据转化成32 bit存入FIFO中。若是单次收集(采样点规则小于16 K),则在收集完结后发生中止,由核算机一次性悉数读回数据;若是接连收集,则当FIFO的可编程近满/PAF标志位有用时,发生中止信号,此刻核算机呼应中止后,仅顺次读取2 K×32 bit的数据,因为收集数据从FIFO中读出比写入的时钟频率高许多,而采样还在持续,因而当/PAF再次有用时,核算机又读取相同的数据量,这样接连循环地进行,直到核算机软件宣布中止指令才完结数据收集进程。

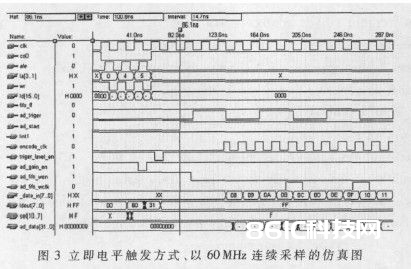

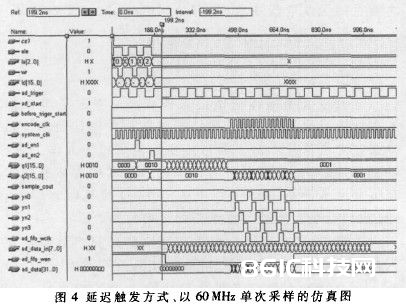

4 时序仿真剖析

时序仿真是挨近实在器材运转环境的仿真,仿真进程中已考虑了器材硬件特性,且时序仿真的网表文件中已包含了较为准确的推迟信息,因而仿真精度很高。

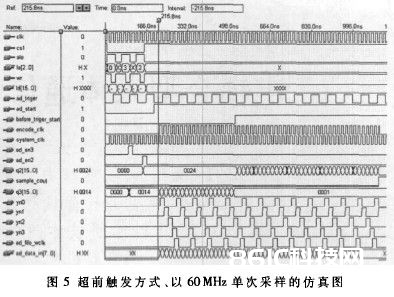

时序仿真环境依照数据收集的进程来树立,完结各种初始化设定后,首要留意触发操控、采样时钟的输出以及数据收集的启/停操控是否满意要求,假如没有到达规划要求,则有必要对前面的规划描绘加以修正,直到符合要求,才能够将发生的下载文件经过编程器或下载电缆载入方针器材FPGA中。仿真成果如图3~图5所示。

从时序逻辑图可知,触发操控、采样时钟的输出以及数据收集的启/停操控满意体系要求。能够将发生的下载文件经过编程器或下载电缆载入方针器材FPGA中。

经测验标明,本文规划的虚拟逻辑剖析仪体系安稳,作业状况杰出,具有了较强的逻辑剖析才能,能满意信号剖析的要求。因为该计划依据Altera公司的EPF10K30E系列FPGA来完结,使部分硬件功用软件化,使硬件电路大为简化,提高了逻辑剖析仪的可靠性,降低了本钱,且功用易于扩展,具有必定的教育和科研价值。