13.2体系作业原理剖析

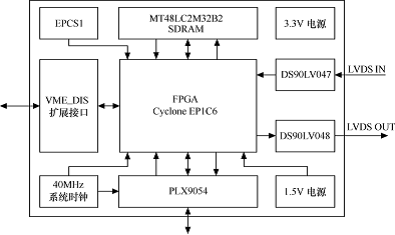

如前所述,一个完好的信号收集体系,除了具有信号输入单元、信号处理单元和信号输出单元外,还需求缓冲区、时钟以及电源等相关体系。如图13.2所示是本事例信号收集体系的结构框图。

图13.2信号收集体系结构框图

该结构图中,方块表明对应的功用部件,连线表明互联联系。它明晰地表明了体系的组成结构及相互联系。首要将分别从3组总线,即数据总线、操控总线和地址总线来知道体系各首要模块之间的联系,再来剖析体系的操控机制和作业原理。

13.2.1数据总线

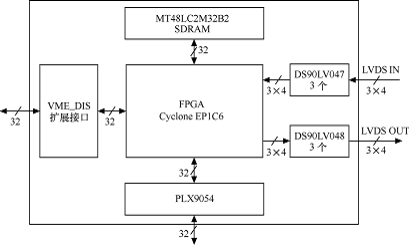

数据总线是体系中传送数据的链路,也是信号收集体系中最重要的链路。各功用部件的性能指标决议了数据总线的宽度及频率。如图13.3所示是本体系数据总线的衔接示意图。

图13.3数据总线衔接示意图

从图中能够看到,数据总线是双向的,也就是说具有了信号输入和信号输出两种用处。

首要看信号输入链路。TTL单端信号经过VME_DIS扩展接口进入体系,可支撑32路单端信号一起收集。LVDS差分信号经过3个DS90LV047接纳器进入体系,可支撑12路差分信号一起收集。两种信号经过FPGA收拾后传输至SDRAM中进行缓存,终究依据PCI9054的传输机制将数据传送至主机内存中。

再看信号输出链路。信号输出链路其实是信号输入链路的逆向进程。信号收集体系能够依据主机端的恳求,将存储于主机上的数据经过PCI总线传输至PCI9054,再经过FPGA操控、收拾、转发至LVDS驱动器DS90LV048输出接口或TTL单端输出接口VME_DIS上。

13.2.2操控总线

操控总线用于FPGA对缓冲区SDRAM以及PCI9054的操控。在FPGA中,能够将这两部分作为两个模块,一个是SDRAM操控器,另一个是PCI本地操控器。经过这两个操控器模块,完结FPGA与它们和谐地作业。

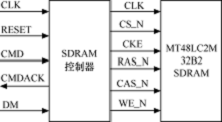

SDRAM操控器是FPGA内部用于操控外部SDRAM读写及改写等操作的逻辑单元。SDRAM操控器的操控总线衔接示意图如图13.4所示。

操控器左面的操控总线包含时钟信号CLK、复位信号RESET、指令信号CMD、指令应对信号CMDACK以及数据有用信号DM等。

操控器右边的操控总线包含时钟信号CLK、SDRAM片选信号CS_N、时钟时能信号CKE、行挑选信号RAS_N、列挑选信号CAS_N以及写使能信号WE_N等。经过SDRAM操控器,用户能够依据需求发送相应的姓名对外部的SDRAM进行操控。

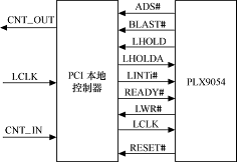

PCI本地操控器是FPGA内部用于操控PCI9054进行参数装备和数据传输的逻辑单元。PCI本地操控器的操控总线衔接示意图如图13.5所示。

图13.4SDRAM操控器操控总线衔接示意图图13.5PCI本地操控器操控总线衔接示意图

操控器左面的操控总线包含时钟信号LCLK、操控输入信号CNT_IN和操控输出信号CNT_OUT等。操控输入输出信号是依据与PCI9054之间的交互发生的,完结了FPGA其他模块与PCI9054的交互操控。

操控器右边的总线则包含了PCI9054供给的本地端装备总线(图中未画出)以及交互时需求运用的操控线。包含了总线操作起始信号ADS#、传输完毕信号BLAST#、本地总线占用恳求信号LHOLD、总线占用应对信号LHOLDA、本地中止信号LINTi#、总线准备好信号READY#、总线读写信号LWR#、时钟信号LCLK以及本地复位信号RESET#。

13.2.3地址总线

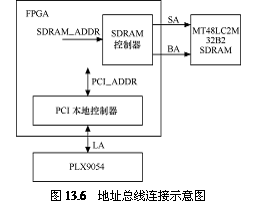

地址总线是存储器材操控器用于对存储空间进行寻址操作的总线,一起也能够完结编码器和译码器的效果,区别不同操作类别。如图13.6所示是本体系地址总线的衔接示意图。

其间,SDRAM操控器经过接纳其他模块发生的地址SDRAM_ADDR,发生SDRAM的行地址SA和列地址BA,完结对SDRAM的存储空间的寻址。这种情况下,地址的改变由FPGA操控。

而PCI本地操控器则经过对PCI9054的本地总线地址线LA进行译码,结合PCI本地操控器的操控总线来区别PCI总线与FPGA之间的不同交互方法。这种情况下,PCI9054完结了地址的映射和增减改变作业。

13.2.4信号收集体系操控机制

首要,将需求收集的信号经过相应的接口接入本体系,构成一组LVTTL信号进入FPGA。因为这一组信号的宽度不决,在将之存入具有32位数据宽度的SDRAM之前,往往需求进行总线宽度的操控。

一般在数据传输的接口操控中,常常选用FIFO或许DPRAM进行数据宽度操控。首要因为两种器材都具有两个数据端口,能够方便地调整前后两级逻辑的数据宽度。

其次,随同数据宽度调整将发生时钟域改换问题。一般直接运用逻辑门建立的数据宽度转化(串并/并串转化)还需求别的进行时钟体系的分配,且难以得到准确同步的时钟。而运用FIFO或DPRAM能够运用独立的时钟对两个数据端口进行操控。

再次,这两种器材均能够运用FPGA内部的逻辑资源建立,无需运用分立元器材,不只降低了本钱也提高了体系的稳定性。

因而在本信号收集体系中运用了DPRAM对数据宽度进行转化。转化得到的32位宽度数据总线被传输至SDRAM中,完结信号输入单元和信号缓存单元的和谐对接。

根据PCI的信号收集体系一般选用的是根据中止的DMA传输。因为PCI总线的建议、占用直至开释需求必定的时刻,因而信号收集体系需求一个缓冲区来确保正在收集的信号被存储起来,直至下一次的PCI总线传输到来而缓冲区不溢出,即数据不丢掉。

本体系中,当SDRAM中缓存的数据到达必定的量级时,FPGA将向PCI9054宣布本地中止,恳求建议DMA传输。主机端捕获中止后,将发动PCI9054的DMA传输,经由PCI本地操控器向SDRAM操控器发送指令,将数据从SDRAM中取出,并传输至PCI9054,终究进入主机内存中。