跟着举动设备印象显现与画质日渐演进,举动设备亦引入8K / 4K等高画质的显现,并运用于拍摄、游戏和用户接口,促进印象传输带宽和速度要求大增。更有大尺度面板也相继供给高画质面板于电视设备上,以4K画质而言,其面板的优势和价值在50吋及以上的电视中更简单表现。日本政府更方案于2020年奥运期间供给8K高画质的视讯转播。在此规划下,面板规范必然也得向上进步。跟着迈向高画质纪元,时序操控芯片 (T-CON Chip; Timing Controller Chip) 也需进步其所支撑的分辨率,处理高画质画面相关数据,从而将完美的画面出现于面板上。

当对画质 (Resolution) 的要求愈来愈高,相对需求处理的数据量也随之进步,以4K画质为例,其分辨率是FHD (2K×1K) 的四倍。为了节约印象传输接口的带宽耗费,因而时序操控芯片内多半会内建SRAM内存,此一内存用来暂存现已传送到时序操控芯片驱动器,但没有要透过时序操控芯片驱动器进行输出的印象数据。因为面板的尺度愈来愈高、分辨率愈来愈高、画面更新率、色泽也都在进步,因而,时序操控芯片内的SRAM内存将不断的加大容量,好因应愈来愈大的印象数据传输量与处理量。

当内建SRAM容量愈来愈大时,相对时序操控芯片制作的本钱也随之添加。更多的SRAM内存容量就意味着更大的芯片面积。且跟着效能与耗电的要求愈加谨慎,芯片的制程也就愈往高阶制程跨进。随同而来的问题,便是芯片良率以及作业牢靠度的影响。先进制程与愈来愈大的内存需求,成为时序操控芯片制作端的不稳定要素。

为保证时序操控芯片上的内存作业正常,内建自我测验技能 (BIST; Built-In Self -Test) 成为芯片实作中,不可或缺的一部分。自我测验电路 (Built-In Self-Test),可以进步测验的过错包括率,缩短规划周期,添加产品牢靠度,并加速产品的上市速度。因为传统的测验做法是针对单一嵌入式内存开发嵌入式测验电路,所以会导致时序操控芯片面积过大与测验时刻过久的问题,从而添加时序操控芯片规划发生的测验费用与出售本钱。别的,传统内存测验办法无法针对一些缺点类型而弹性挑选内存测验的算法,将导致内存测验成果不精确。有鉴于此,厚翼科技特别开发「整合性内存自我测验电路发生环境-Brains」,以处理传统规划之缺乏。本文将针对时序操控芯片运用,结合厚翼科技所开发之「整合性内存自我测验电路发生环境-Brains」,调配实作事例跟读者们共享。

实作事例

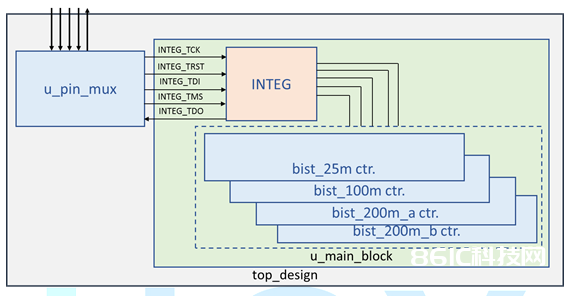

以下将以时序操控芯片运用实作事例,介绍怎么透过Brains主动化发生相关内存测验电路,以处理内存所形成良率下降问题。此事例所运用的制程为130nm,图一是该事例简略架构图,此架构明确地将芯片IO部分与首要功用部分切开来,并透过Pin Mux功用,来节约芯片顶层所需的操控脚位。在首要功用部分,共有四个Clock Domain,各异Clock Domain下,各自包括了不同品种的内存于其间。针对这些内存,咱们透过Brains主动化的发生相对应之内存测验电路。

图一 T-CON事例简略架构图

此事例中,针对内存测验的需求,包括了:全速测验形式 (At-Speed Testing),Bypass功用以及主动分群 (Auto Grouping)。其间的Bypass功用,首要是用来进步DFT Test Coverage。当透过Scan Chain做测验时,因为无法观测到内存内部数值,所以全体芯片Test Coverage会受影响。Brains所支撑的Bypass功用,便是用来补足此点。该功用将内存的输入端及输出端进行异或处理,并可依据需求,挑选是否运用缓存器来贮存数值。藉此,可在Scan Chain测验形式下,进步全体芯片Test Coverage。

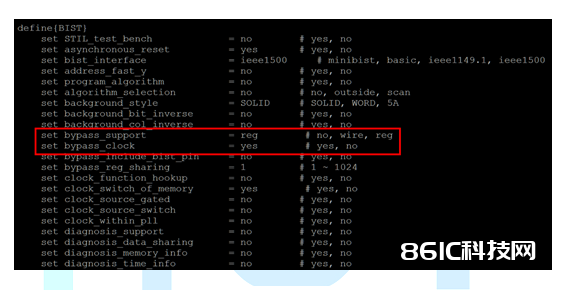

因为不同的规划项目及运用,关于内存测验的需求不尽相同。因而,Brains将不同的规划需求,以选项的方法出现。运用者可依据不同的需求,挑选所需的功用。图二为Brains功用挑选典范档案 (Brains Feature List, BFL)。其间赤色框线的部分,便是用来挑选Bypass功用是否要支撑。

图二 Brains功用挑选典范档案

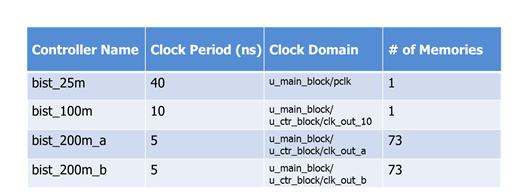

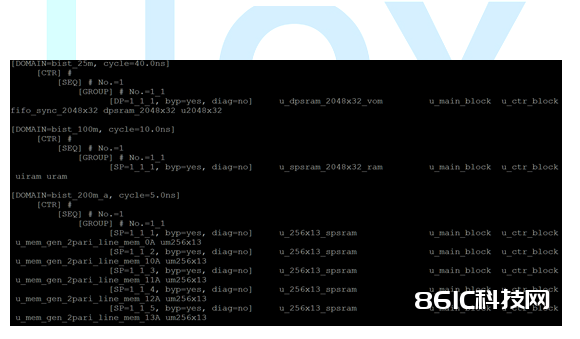

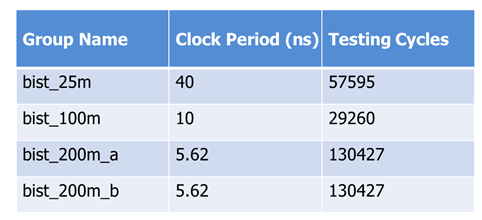

此事例一共运用到148个内存,其类型包括了Single-Port SRAM,Dual-Port SRAM以及Two-Port SRAM。透过Brains所支撑的内存主动辨识功用,用户只需将内存模块的Behavior Model (Verilog file) 指定到Brains中,则可轻易地将规划项目中所用到的内存模块辨识出来。再调配Brains所支撑的Clock Tracing功用,从内存模块的Clock信号,往上层追溯,直到该规划项目的Clock Root点,即可主动地将内存模块归类到各自所属的Clock Domain下。表一为主动分群之后的分群架构,共有四个BIST Controller,各异针对其所属之内存模块来进行操控与测验。而具体的分群架构,则会记载在Brains所产出之BRAINS_memory_spec.meminfo档案中,该档案记载各个BIST Controller中,关于Sequencer和Group的架构,如图三所示。

表一 内存主动分群成果

图三 BRAINS_memory_spec.meminfo典范档案

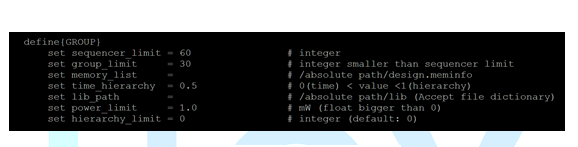

由图三可得知,单一Clock Domain下,会包括Controller, Sequencer等架构,而Sequencer下则会依据BFL中关于Group的界说来区分Group的架构,相关设定如图四所示。其间sequencer_limit选项用来设定单一Sequencer下,所支撑最多Group数。而group_limit选项则是用来设定单一Group下,所支撑最多内存模块数目。

图四 BFL中Grouping相关设定

实作成果

当Brains履行结束后,则会发生相对应档案。其间包括BIST 电路档案 (Verilog file) 、相关组成模仿履行档案 (TCL file) 以及参加BIST电路后的无缺规划档案 (Final RTL Design; Verilog file)。图五为参加BIST电路后,无缺的规划项目架构。

从图五可得知,此实作事例最终会由一组JTAG接口,来操控整个BIST测验的流程。单一JTAG接口的操控方法,可节约芯片顶层的脚位数目,且规范JTAG接口,也便利与其它功用整合。

图五 实作成果架构图

当相关电路发生结束后,需求透过仿真来验证功用性是否无缺。Brains除了发生相对应的仿真程序外,也会额定发生包括有Fault Bits的预先埋错内存模块 (Faulty Memory Model)。此预先埋错内存模块首要用来验证Brains所发生的BIST电路功用正确与否。表二为各个Clock Domain履行模仿验证时所需花费的时刻。

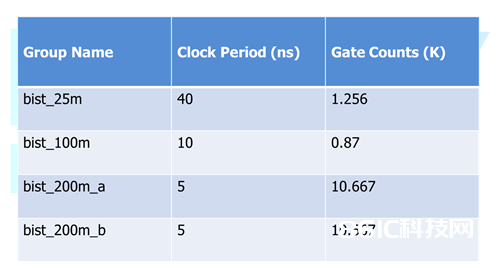

除了仿真时刻之外,所发生的BIST电路面积,一般也是芯片规划实作中,考虑的要素之一。表三为BIST电路组成完之面积成果,悉数的BIST电路占约23K Gate Counts。以此事例之T-CON芯片所含148个内存数目来比,BIST电路所占之芯片面积适当藐小。

表二 模仿时刻成果

表三 BIST电路面积成果

总结

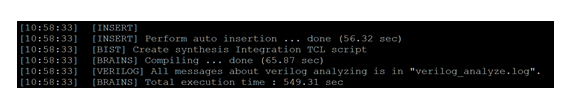

因应高画质代代降临,时序操控芯片内含之内存数量必然愈来愈多,此刻,内存测验处理方案亦成为芯片规划中不可或缺的一环。藉由Brains主动化发生相对应的内存测验电路,对用户来讲,不需过分繁复的设定进程,即可完结内存测验处理方案的实作。以此事例为例,单纯Brains运转的时刻,只需约九分钟的时刻 (如图六所示) 就能完结内存测验处理方案的实作。关于争分夺秒的AS%&&&&&%实作时程来说,可节约适当大的时刻。除此之外,Brains弹性的设定选项,以及根据自有专利所建构的硬件电路,都是用户在实作内存测验处理方案的一大利器。

图六 Brains实作时刻信息

关于厚翼科技

厚翼科技根据多项内存测验相关专利,致力于立异的各类的内存测验技能的研制,以便对全球快速生长的体系芯片架构供给更牢靠的内存测验服务。如今各种电子产品功用日趋杂乱,体系芯片规划需求更多的内存,体系芯片规划厂商正面临着产品对本钱与节能等各方面的需求。厚翼科技所立异的可程序化暨管线式架构内存测验技能供给给用户可以建构出特有的优化内存测验方法。厚翼科技的核心技能在于特有的可程序化暨管线式架构内存测验技能,而且透过各项专利加以维护。厚翼科技可以和运用者严密协作与供给技能支撑,以便帮忙运用者完结高质量规划,添加产品竞赛力。 展望竞赛剧烈的电子体系产品商场,当你方案架构新的体系芯片运用产品时,厚翼科技凭仗其高效能、低功耗可程序化暨管线式架构内存测验技能,可以帮忙你的团队有用的操控产品本钱,打败竞赛对手。