1.概述

功率MOSFET开端是从MOS集成电路发展起来的,它经过添加源漏横向距离进步器材耐压,然后完成集成电路中高压驱动。功率MOSFET已很多使用于电力电子,消费电子、轿车电子和水声工程等范畴。尽管功率MOSFET具有效率高、结构简略、便于数字化操控等长处,可是其选用的电力电子器材对过压过流的承受才能较差,简略焚毁,因而维护电路的规划非常重要,而且要求维护呼应时刻做到微秒级。功率MOSFET维护主要是指过流维护,关于过压的状况一般选用吸收电路来进行按捺。

在水声发射机功率MOSFET的规划和运用中,常常因为输入信号的反常和环境搅扰,而导致功率放大器简略焚毁。

针对功率MOSFET易受损或烧坏的状况,在水声发射机使用中专门规划了一种以CPLD(杂乱可编程逻辑器材)为中心器材的可编程维护电路。现在CPLD现已得到广泛使用。它具有体系结构/逻辑单元灵敏、处理速度快、集成度高、可完成较大规划电路、编程灵敏、规划开发周期短、规划制作成本低、开发工具先进、规范产品无需测验、质量安稳、可实时在线查验以及适用范围广等长处,因而逐渐被使用于各类维护电路规划中。

鉴于CPLD的许多长处,本规划选用独自CPLD芯片为中心,不需要单片机或DSP进行操控,来处理以MOSFET为中心的大功率发射机鼓励信号反常或毛病所带来的严重问题,为发射机的MOSFET电路的安全安稳运转起到维护效果。CPLD维护电路在输入高电平长脉冲、接连信号和短周期脉冲等典型反常信号状况下,经过简略改动代码参数就能够防止反常的信号进入到后级损坏功率MOSFET,完成对电路的维护效果。

2.功率MOSFET基本原理

功率MOSFET电路的基本原理是:选用V1,V2,V3和V4四只可关断的功率器材组成一个H桥型丁类开关放大器(如图1所示)。图1中,对角的2只功率器材(V1和V4,V2和V3)一起导通和关断。同一侧(V1和V2,V3和V4)的器材替换导通和关断,且鼓励信号相差180.这样,当上边的器材关断(导通)时,下边的就导通(关断)。因而输出A,B两点的电位依照输入鼓励信号设定的频率(或脉宽),轮流在电源的“+”和“-”之间切换。

功率MOSFET在实践使用过程中,电路上存在高电压和大电流,而且回路上的散布%&&&&&%和散布电感都很大,功率器材门极鼓励信号稍有毛病就会在功率回路上引起过电压(或过电流)而焚毁设备或器材。所以,这种功率放大器不只要有齐备的过压过流维护功用,更重要的是要求输入至功率放大器桥路上的功率器材门极鼓励信号安稳牢靠[4]。

3.维护电路CPLD完成

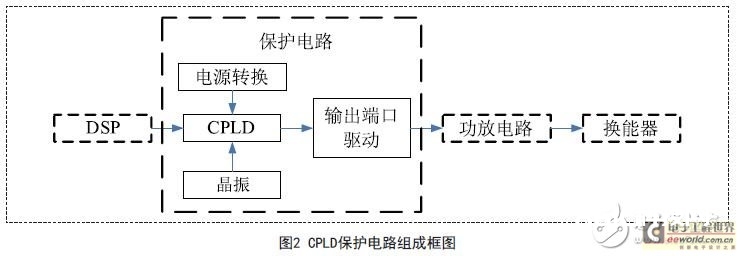

CPLD维护电路的内部主要由电源转化,晶体振荡器,CPLD,输出端口驱动等部分组成。

维护电路组成框图如图2所示。

维护电路的中心部分主要是一个CPLD,一切的功用都是经过对此器材进行逻辑编程来完成。硬件上是对来自DSP电路的模仿输出脉冲进行信号转化和维护,对应的输出为两路驱动信号和一路包络信号。两路输出信号包络相同,时刻同步,信号凹凸电平相反。包络信号便是两路输出信号的包络,时刻同步。两路输出信号经过光隔阻隔并反相后为功率MOSFET供给发射鼓励信号源,包络信号经光隔后为功率电路供给操控信号。

CPLD维护电路主要对输入MOSFET电路的典型反常信号,包含接连波信号、短周期脉冲信号和高电平长脉冲信号进行输入维护。一切反常输入信号一般由这三种信号组合而成。假定接连波信号是超越10ms脉冲宽度的信号;短周期脉冲信号是小于200ms脉冲周期的信号。对其他不同参数反常信号的处理,可经过简略设置软件计数器来改动。维护电路软件流程图如图3所示。

维护电路的详细维护功用与时序图如下所示:

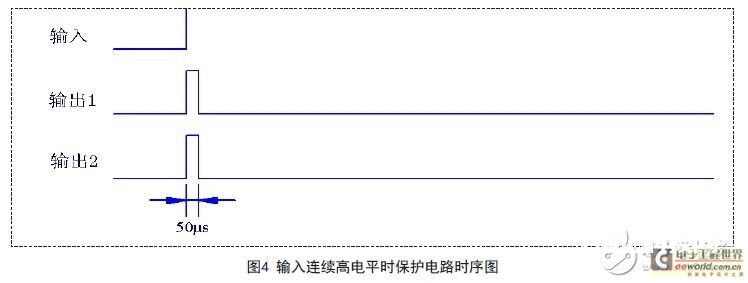

当DSP电路给维护电路输入接连高电平,维护电路会以榜首个上升沿为基准,开端检测10kHz频率信号的榜首个周期(即100μs),假如没有下跳沿,维护输出50μs长高电平后,封闭输出端口,坚持低电平,两路驱动信号输出和输入时序如图4所示。

若DSP电路给维护电路输入接连波形信号,维护电路将会以榜首个上升沿为基准,每隔200ms输出一个10ms的脉冲波,防止接连作业损坏功率MOSFET,两路驱动信号输出和输入信号时序如图5所示。

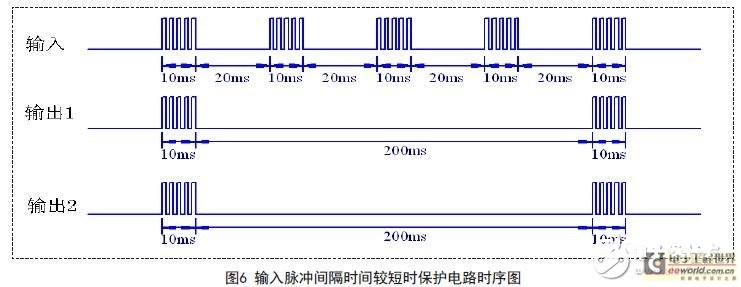

若输入信号两脉冲之间的距离小于200ms,维护模块在榜首个脉冲输入之后将会操控200ms的时刻,坚持在这200ms以内继续低电平后康复正常,呼应下一个脉冲信号的到来,以脉冲信号的周期为20ms为例。两路驱动信号输出和输入时序如图6所示。

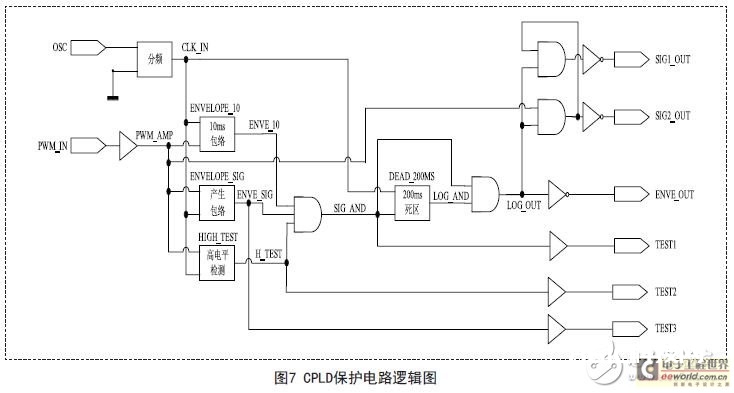

CPLD维护电路完成的逻辑图见图7所示。

OSC-晶振输入信号;PWM_IN-输入脉冲信号或许反常搅扰信号;SIG1_OUT-输出信号1;SIG2_OUT-输出信号2;ENVEOUT-操控信号;TEST1-10ms包络信号、输出信号包络和高电平检测信号的与;TEST2-高电平检测信号;TEST3-信号包络检测信号。SIG1_OUT、SIG2_OUT和ENVEOUT信号进入MOSFET功率管驱动芯片输入端,其输出是MOSFET的输入信号。

图7中三角形符号输出表明的是对输入信号增强驱动才能;矩形表明的是逻辑模块;其他图形标识的是输入输出和逻辑符号。逻辑图的五大功用模块介绍如下:

①分频模块:

该模块的功用是起到分频效果,确保每个模块在做延时的时分差错坚持在要求的范围内,还能够确保占用体系资源很小。

②10ms包络模块:

该模块的功用是使输出信号的脉冲宽度不会大于10ms,依据时钟频率发生一个10ms的包络信号与信号包络模块的输出信号相与,就会得到一个10ms的包络,在没有信号输入的状况下,输出为低。

③依据信号发生包络模块:

该模块的功用是依据输入信号,输出一个与输入信号同相位的包络信号。没有信号输入的状况下,输出为低。

④接连高电平检测模块:

该模块的功用是检测输入信号是否是接连高电平,假如是接连高电平,使输出为一个脉宽很窄的信号,然后拉低,在没有信号输入的状况下,输出为低。

⑤200ms死区模块:

该模块的功用是发生一个200ms的死区,即输出有200ms的时刻为低电平,该模块是依据信号的下降沿来动身的,当输入信号下降沿到来的时分,输出拉低,并坚持200ms时刻,200ms往后,输出置高。

4.实验验证

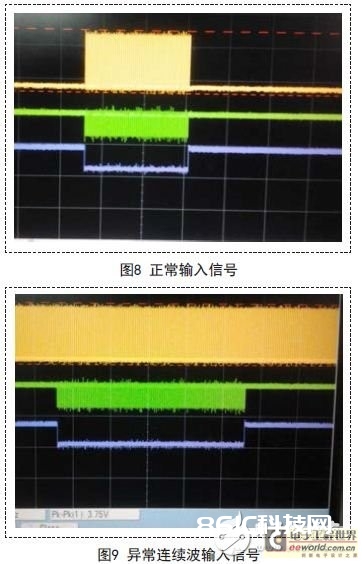

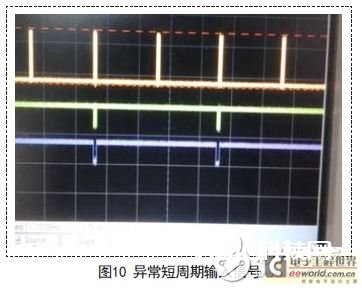

在功率MOSFET维护电路输入端别离输入正常信号、接连高电平、接连波信号和短周期的脉冲信号。在没有维护电路的状况下,若输入端输入这几种反常信号,发射机功率MOSFET电路必将焚毁。维护电路输出经光隔阻隔并凹凸电平转化后驱动MOSFET作业。在实验室状况下,各种状况的正常、反常输入信号经CPLD维护电路后输出信号实测波形如图8~11所示。

榜首路是原始输入鼓励信号,第二路是维护电路的输出信号,第三路是包络信号。

由图中可知,反常信号经CPLD维护电路逻辑处理后,输出满意体系要求而且使功率MOSFET能够承受的输入信号。

5.定论

本文提出了选用CPLD芯片处理大功率发射机鼓励信号反常或毛病带来严重损害的办法。经过体系模仿测验以及实践拷机测验,验证了本规划的正确性和可行性。现已将此规划使用于某大功率发射机项目的维护电路中,最大极限减小了因鼓励信号反常和毛病给发射机带来的损害。别的,本规划的硬件电路具有较强的通用性,只需稍加改动软件编程,就能够使用于其他电路的信号处理规划中。