赛灵思UltraScale架构的增强功用结合Vivado规划套件的省时东西能协助您更快打造超卓体系。

许多商场和运用都对体系带宽和处理功用需求显着增加。无论是有线或无线通信、数字视频仍是图画处理,更高的数据吞吐量要求都完成相同的成果,那便是一切体系组件的流量和要求都在进步。通过并行和串行I/O抵达片上的数据也越来越多。数据有必要通过缓存,然后再次以DDR存储器方式通过并行I/O或以串行存储器规范(如混合内存立方体(HMC)和MoSys 带宽引擎)方式再次通过串行I/O。数据从并行和串行I/O回来后,在传送到下个目的地之前有必要在逻辑和DSP中进行处理。

因为许多原因,体系处理要求越来越杂乱。以更高数据速率传输的更大数据包要求并行数据总线更宽,并且频率更高。为高效处理数据,往往要在单一器材上构建整个体系,然后防止因两个FPGA之间发送许多数据引起的相关时推迟和功耗问题。因而需求更密布的具有更多功用的FPGA。重要的是,在进步高功用FPGA运用率的一起,有必要坚持能以最高功用运转,以防止器材填充时功用下降。

让杂乱的高容量器材完成高运用率听起来或许对规划人员来说是一项很艰巨的使命。赛灵思供给了许多处理方案,旨在缩短规划时刻,让规划人员集中精力完成产品差异化,然后从商场中锋芒毕露。

结合运用高功用并行SelectIO和高速串行收发器衔接功用,可在UltraScale FPGA之间完成数据传输。

ULTRASCALE架构

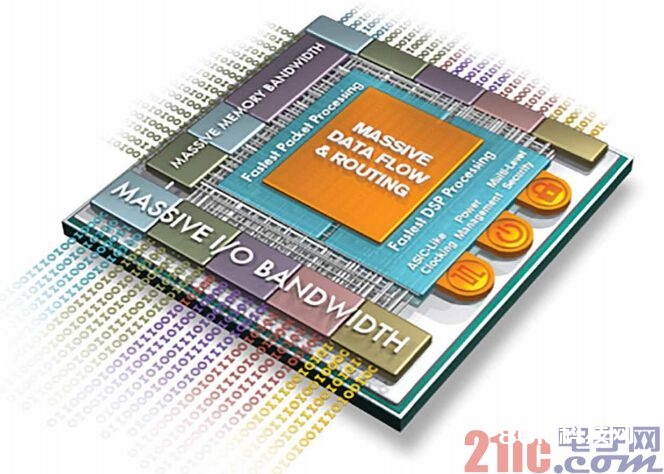

为了处理普遍存在的商场难题,赛灵思近期推出了UltraScale™架构(如图1所示),可供给史无前例的体系集成度、高功用和超卓的功用。赛灵思用这款全新架构创立了两款高功用FPGA系列产品。赛灵思 Virtex® UltraScale与Kintex® UltraScale系列相结合,能满意多种不同体系要求,侧重通过许多技能立异与前进下降总功耗。UltraScale技能同享许多构建块,能供给可扩展的架构,并针对多种不同的商场需求精心优化。

增加体系带宽

在进行任何信号处理或数据操作之前,数据首先要抵达目的地。现在已有许多串行和并行协议和规范专门满意方针运用的特定需求。大多数规范的一个一起主旨便是进步全体数据吞吐量,然后支撑许多信息以越来越高的速数据速率进行体系传输。

图1 –UltraScale架构的首要优势在于速度和带宽。

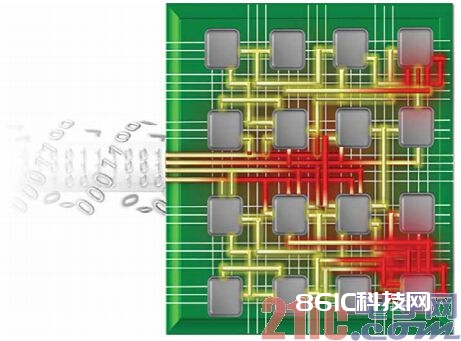

图2 – UltraScale架构能处理许多数据。

结合运用高功用并行SelectIO和高速串行收发器衔接功用,可在UltraScale FPGA之间完成数据传输。I/O模块通过灵敏的I/O规范和电压支撑可完成先进的存储器接口和网络协议。UltraScale架构中的不同串行收发器数据传输速率高达16.3 Gbps,能供给干流串行协议所需的一切功用,最高支撑32.75 Gbps,能满意25G+背板规划的要求,相对于前一代收发器而言能大幅下降单位比特的功耗。UltraS-cale FPGA中的一切收发器都支撑PCI Express® Gen3和Gen4所需的数据速率,而PCI Express的集成块则支撑依据UltraScale架构的FPGA,最高能支撑x8 Gen3端点和Root Port规划。

数据时钟功用与缓冲

一切同步体系都要依托一个或多个时钟信号来完成电路同步。体系功用进步要求以更大器材容量进步时钟频率,并要求改善时钟灵敏性,下降总时钟功耗。

UltraScale架构选用功用强壮的通过从头架构规划的时钟办理电路体系,包含时钟归纳、缓冲和路由组件,能供给功用强壮的结构,满意规划要求。时钟网络支撑FPGA中极为灵敏的时钟散布,然后能最大极限地削减与时钟信号相关的偏移、功耗和推迟。此外,时钟办理技能紧密结合专用存储器接口电路体系,可支撑DDR4等高功用外部存储器。时钟细分和新式门控时钟粒度技能相对于现有的FPGA而言能进一步加强对时钟功耗的操控。

相对于前一代FPGA以及同类竞争性FPGA,大局功用时钟缓冲器数量的大幅增加有助于显着进步规划人员的生产力。此前,大局缓冲器的运用要十分节约,FPGA中心只要32个大局时钟缓冲器。UltraScale架构能在架构中自在散布大局功用时钟缓冲器,然后在需求时就能供给资源,不必再那么节约了。此外,赛灵思相对于前一代FPGA而言大幅简化了时钟缓冲器类型,且保留了一切时钟切换、时钟分频和时钟使能功用,然后取得许多灵敏的高功用时钟缓冲器,能在需求时供给悉数功用。

数据的存储、处理和路由

任何体系的要害都在于其处理、操作和转化接收到的数据的才能(如图2所示)。体系杂乱性的进步,要求将通用架构与更专业的功用(专门针对详细类型的数据处理)相结合。

现在的FPGA架构集成许多组件:含有六输入查询表(LUT)和触发器的可装备逻辑块(CLB)、带27×18乘法器的DSP Slice、带内置FIFO和ECC支撑的36Kb Block RAM等。这些资源通过许多的高功用、低时延互联紧密衔接在一起。

除了逻辑功用之外,CLB还供给移位寄存器、乘法器和进位逻辑功用,并能装备LUT为散布式存储器来合作高功用可装备Block RAM。DSP Slice(包含全新的96位宽XOR功用、更宽的27位预加法器和30位输入)履行许多独立功用,其间包含乘法累加、乘法加法和形式检测等。除了器材互联之外,在选用第二代SSI 3D%&&&&&%技能支撑的器材中,信号可选用专用低时延接口模块在超级逻辑区域之间传输。这种整合的路由资源能方便地支撑下一代数据总线宽度,然后让器材运用率到达90%以上。

图3 – UltraScale器材为业界抢先的科技增加常用功用。

简化规划应战

UltraScale架构带来的架构增强功用可协助规划人员在相同区域打包更多规划方案,但一起器材尺度也在增大。,其成果便是单器材能载入更多规划,这是一大优势,但也给规划团队带来了巨大压力,有必要快速完成指定规划,然后让终究产品尽或许快的上市。运用UltraScale架构和协同优化的Vivado®规划套件,赛灵思可以打造出多个省时、生产力更高的处理方案。

集成中心功用

高度灵敏的可编程性这一极具价值的功用与许多作业相同,要想有所得就要付出代价。运用可编程资源构建的功用或许比专门针对该功用的模块尺度更大,甚至或许速度更慢。当然,FPGA本质上显着的优势便是具有可编程性,但赛灵思FPGA完成了专门功用、集成IP的

恰当平衡,能协助用户快完成常用功用(图3)。UltraScale架构包含针对常见通信协议的集成模块。Kintex UltraScale和Virtex UltraScale器材中包含针对PCI Express、100G Ethernet和150G Interlaken的多个集成模块,且都通过全面测验和验证,能保证完成功用。

除了通信协议之外,每个I/O Bank都包含一个可编程存储器PHY,能用存储器接口生成器(MIG)东西进行装备。这充分说明了依据需求进行集成的特性。存储器PHY和一些操控逻辑可创立为可编程专用函数,但存储器接口的数字部分用器材架构构建,针对不同形式供给一切必需的定制与支撑,而这则是专门电路所难以完成的。

在器材架构中有许多其它模块,专门规划用于履行特定功用,一起坚持可编程性。规划人员能以不同深度和广度来装备这些模块存储器,以级联成更大型的低功耗阵列。DSP Slice具有许多形式,能让用户依据所选功用拜访模块的不同组件。因而除了门和寄存器之外,UltraScale架构上能完成许多丰厚的功用。

可定制、可重复的IP能进步生产力

每个规划都包含许多不同架构构建块,相互衔接构成体系。职业内有些功用现已十分齐备了,从经济性视点讲完全可以将它们做成专用的固定功用模块。但是,最佳规划办法是选用可编程逻辑构建功用,并通过验证,随时按需重用。这种IP概念现已存在了许多代,但赛灵思近期推出了一些生产力增强特性(图4)。

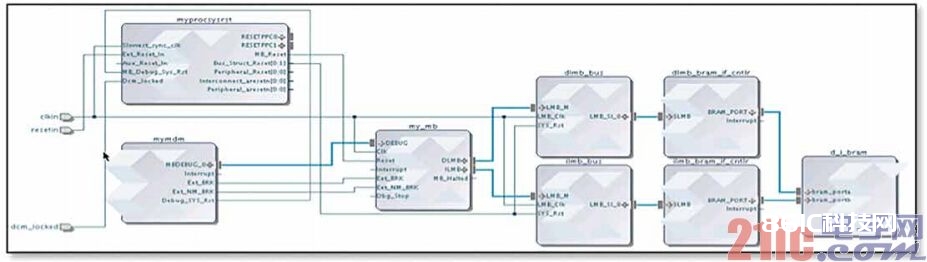

图4 – Vivado东西加速杂乱规划的创立和完成。

即插即用IP

2012年,赛灵思选用ARM®AMBA® AXI4接口作为即插即用IP的规范接口。选用一致的规范接口比较曩昔能大幅简化IP集成,将多种不同接口整合到一个,规划人员也不必去把握多种不同的接口。UltraScale架构持续获益于AXI4互联的灵敏性和可扩展性,然后协助规划人员完成最快的产品上市进程,一起选用AXI4-Lite和AXI4-Stream等不同AXI4互联协议优化IP功用、面积和功耗。

Vivado IP Packager和IP Catalog选用IP-XACT规范(该规范开始由SPIRIT联盟作为东西流程中封装、集成和重用IP的规范结构推出)。IP-XACT现已取得IEEE的同意(IEEE1685-2009)。Vivado IP Packager选用在本地或同享驱动器上可扩展IP Catalog中供给的束缚、测验渠道和文档来创立规划。选用Vivado IP Catalog,用户可以将自己的IP、赛灵思的IP以及第三方IP无缝集成在一起,然后保证规划团队轻松一致地共享一切IP。

VIVADO IP INTEGRATOR

Vivado IP Integrator(Vivado IPI)(图5)是以IP为中心的规划流程,可加速体系集成进展,更轻松方便地将不同组成部分组成成体系。运用交互式图形用户界面,IPI供给IP接口的智能主动衔接、一键式IP子体系生成和强壮的调试功用,可协助规划人员轻松方便地衔接其IP Catalog中的任何甚至悉数IP。这种功用使得规划人员能快速拼装杂乱体系,包含来自多种来历的规划资源——一些免费的、一些购买的、一些内部创立的——并且能清楚把握一切构建块都能得到正确装备。从概念到调试从未如此神速。

简而言之,UltraScale架构在许多要害方面进行了架构立异,能成功满意下一代高功用规划的严格要求。像UltraScale这样,能保证运用体系频率越来越高的宽数据总线来完成规划,是成功展开规划作业的必要组成部分。不过,跟着器材尺度和杂乱度的进步,协助规划人员不断进步生产力变得至关重要。赛灵思供给集成块和预验证IP组合,能为规划人员带来加速完成超卓处理方案所需的悉数东西。

图5 – 在IP Integrator中构建规划方案和衔接IP块相同简略。