1.导言

在一些试验、研讨中,有时需求存在相位差的两同频信号。一般选用移相网络来完结,如阻容移相,变压器移持平。选用这些办法有许多不足之处,比方:输出波形受输入波形的影响,移相操作不便利,移相视点随信号频率和所接负载等要素的影响等。若选用直接数字频率组成及数字移相技能,能得到频率及相位差高度安稳准确的信号且完结便利。

2.波形及移相波形发生器的体系组成原理

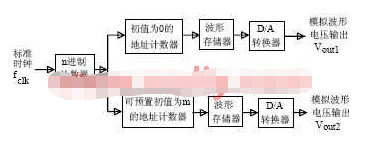

如图1所示为波形及移相波形发生器的体系组成方框图。

图1 波形及移相波形发生器的体系组成原理框图

规范时钟(由晶振电路发生)加于进制可编程的n进制计数器,其溢出脉冲加于可预置初值的地址计数器,生成波形存储器所需的地址信号,地址信号的发生频率正比于时钟频率,且循环往复地改动,然后使波形数据存储器输出周期的正弦序列,D/A转换器则输出接连的模仿正弦电压(或电流)波形,如图2所示。

为移相便利,设一周期的正弦波共采样360个点,即波形数据存储器共存储360个正弦波形的数据。因为移相波形的地址计数器的第一次运转初值为m,故两正弦波存在相位差为 m°。相邻采样点有n个规范时钟脉冲距离,即 T0=N-1/Fclk。图1中波形数据存储器的悉数数据被读出一次的频率为: F=1/T0-360=Fclk/n-360。改动n和m,即可改动输出信号的频率和相位。若时钟频率 Fclk为100MHz,则 。例如取n为1000,m为120,则发生相位为120°,频率为277.8Hz的正弦信号。当n=1时得最高信号频率为277.8KHz。

3.体系的软硬件规划

FPGA是20世纪90年代发展起来的大规模可编程逻辑器材,跟着EDA技能和微电子技能的前进,FPGA的时钟推迟可到达ns级,结合其并行作业办法,在超高速、实时测控方面有十分宽广的使用远景,并且FPGA具有高集成度、高可靠性,简直可将整个规划体系下载于同一芯片中,完结所谓片上体系,然后大大缩小其体积。为此,规划了一种根据FPGA的高精度数字式移相正弦波信号发生器,该设备能够发生频率、相位、起伏均可数字式预置并可调理的两路正弦波信号。相位差规模为0~359°,步进为1°。体系选用Xilinx公司的SpartanⅡ系列XC2S100E-6PQ208E现场可编程门阵列芯片。该芯片最高时钟频率能够到达200MHz,作业电压为2.5V,选用0.22μm/18μm CMOS工艺,6层金属连线制作,体系门数量为10万,CLB阵列数量为20×30,Block RAM容量为40Kbit,最大用户I/O数量为202个。

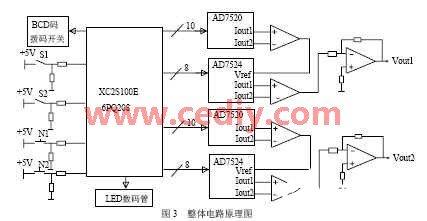

使用FPGA内部Block RAM用来存储一周期的正弦波的360个采样点的数据,每个数据为8位,用一片8位A/D转换器AD7524来输出正弦波,再用一片10位A/D转换器AD7520的输出作为AD7524的参阅电压,用来数字调理输出正弦波的起伏。另一路移相正弦波的发生选用相同的电路结构。全体电路原理图如图3所示。其间LED数码管用来显现输出信号的频率、相位差和起伏。BCD拨码开关用来对频率、相位和起伏值的预置。两按钮别离用来对频率、相位和起伏值的向上和向下调理。为节约硬件开支和FPGA的I/O口线,用一个2位拨码开关来设定显现、预置和调理的状况,即频率、相位差和起伏三个状况。

体系选用硬件描绘言语VHDL按模块化办法进行规划,共分为频率、相位差、起伏预置调理操控模块、正弦波形及移相波形发生模块、显现模块及顶层模块等。经过Xilinx ISE 5.2软件开发渠道和ModelSim Xilinx Edition 5.6 XE仿真东西,对规划文件自动地完结逻辑编译、逻辑化简、归纳及优化、逻辑布局布线、逻辑仿真,最终对FPGA芯片进行编程下载。限于篇幅,这儿仅介绍正弦波形及移相波形发生模块的规划办法(完好程序可向作者讨取)。该模块分为二个进程。其部分程序如下:

process (clk)

variable temp: std_logic:=‘0’;

begin

if rising_edge(clk) then

if temp=‘1’ then v《=v1; temp:=not temp;v11《=d;

else v《=v2;temp:=not temp;v12《=d;

end if;

case v is –以下when句子为360个正弦波形的数据ROM表,这儿只给出了首末几个。

when “000000000”=》d《=“10000000”;when “000000001”=》d《=“10000010”;

when “000000010”=》d《=“10000100”;when “000000011”=》d《=“10000111”;

……

when “101100100”=》d《=“01110111”;when “101100101”=》d《=“01111001”;

when “101100110”=》d《=“01111100”;when “101100111”=》d《=“01111110”;

when others=》 null;

end case;

end if;

end process;

process (clk)

variable count,coun,b: integer range 0 to 277778;

begin

if rising_edge(clk) then

if sw=‘0’ then sign《=‘1’;

else –使用减法完结除法运算。

if coun《277778 then coun:=coun+n;b:=b+1;–信号n由频率预置、调理模块送来。

else

if count=b then count:=1;

if sign=‘1’ then v1《=“000000000”;v2《=m;sign《=‘0’;end if;–信号m由相位预置、调理模块送来。

if v1=“101100111” then v1《=“000000000”;else v1《=v1+1;end if;

if v2=“101100111” then v2《=“000000000”;else v2《=v2+1;end if;

else

count:=count+1;

end if;

end if;

end if;

end if;

end process;

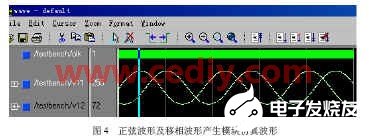

对该模块使用ModelSim Xilinx EdiTIon 5.6d XE仿真东西进行仿真的波形如图4所示。

4.结束语

本规划根据FPGA的高精度数字式移相正弦波信号发生器,充分使用VHDL硬件描绘言语便利的编程,进步开发功率,缩短研制周期,并且体系的调试便利,修正简单。试验标明体系发生的波形安稳,抗干扰能力强,频率、相位和起伏调理便利,精度高,有必定的开发及出产价值。

责任编辑:gt