频率组成技能迄今已阅历了三代:直接频率组成技能、锁相环频率组成技能、直接数字式频率组成技能。直接数字式频率组成(Direct Digital Frequency Synthesis,DDFS或DDS)是第三代频率组成技能的标志,他的首要特色是计算机参加频率组成,既可以用软件来完成,也可以用硬件来完成,或二者结合。直接数字式频率组成器的最大长处便是频率切换的速度极快(可达几微秒),并且频率、相位和起伏都可控,输出频率安稳度可达体系时钟的安稳度量级,易于集成化,更首要的是因为计算机参加频率组成,故可充分发挥软件的效果。

本文首要介绍的是依据单片机和CPLD完成直接数字频率组成详解,详细的跟从小编一起来了解一下。

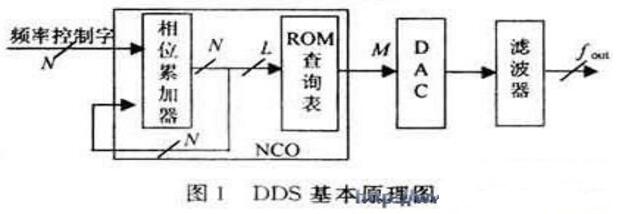

一、DDS作业原理

DDS作业原理框图如图1所示,其实质是以参阅频率源(体系时钟)对相位进行等可控距离的采样。由图1可见,DDS包含由相位累加器和ROM查询表构成的数控振动源(NCO)、DAC以及低通滤波器(LPF)3部分。在每一个时钟周期,N位相位累加器与其反应值进行累加,其成果的高M位作为ROM查询表的地址,然后从ROM中读出相应的起伏值送到DAC。低通滤波器LPF用于滤除DAC输出中的高次谐波。因而经过改动频率操控字K就可以改动输出频率fout。简单得到输出频率fout与频率操控字K的关系为:fout=Kfc/2N,其间fc为相位累加器的时钟频率,N为相位累加器的位数。界说当K=1为体系频率分辨率,即。

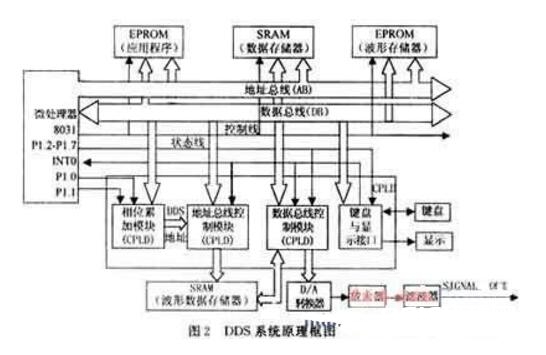

二、体系的整体规划

体系的原理框图如图2所示,本体系首要由单片机部分、DDS主通道部分、键盘及显现部分以及输出信号调度等部分组成。

单片机芯片选用的是比较常见的AT80C31芯片。一起片外还各扩展了1片程序存储器2764与数据存储器6264,别离用来寄存作业中所需的程序与随机数据。

DDS主通道部分是咱们规划的要害所在,该部分首要由相位累加模块、地址总线操控模块、数据总线操控模块与波形数据存储器EPROM、SRAM等组成。其间相位累加模块、地址总线操控模块和数据总线操控模块都是在CPLD上完成,选用的芯片是ALTERA公司的FLEX10K系列器材。咱们将所需求组成的波形采样数据固化在EPROM 2764中,可是咱们知道EPROM的读周期比较长,很难满意体系的拜访时刻要求。因而规划中又运用了1片HSRAM,在DDS体系组成波形的进程中,替代ROM进行波形数据的快速查询。

键盘和显现部分是体系和用户进行交互的重要手法。这一部分的逻辑功用,也是在CPLD上完成的。

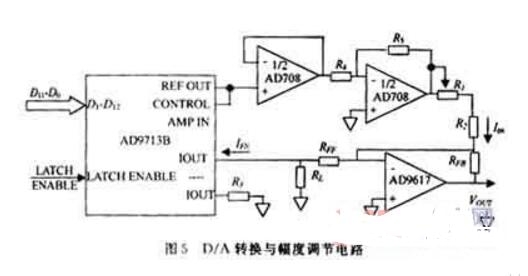

输出信号调度部分是把从HSRAM中读出的波形的数字起伏值首要转化成模拟信号,然后再进行扩大、滤波处理后输出。这一部份包含D/A转化器、起伏扩大器和滤波器。DAC器材选用AD公司的12位AD9713B,该器材特色是具有较高的更新速率(100 MSPS)和较低的功耗(725 mW),因而特别适合于DDS信号组成。起伏调度电路运用的是双极性扩大器AD708、AD9617和AD9713所组成的电路。

三、体系整体作业状况阐明

前面现已提到过,因为EPROM的读取时刻比较长,很难满意体系对时刻的要求,因而在体系中又增加了1片高速SRAM,作为波形数据缓存器。这样,体系就有两个作业状况:首要,体系开端作业时,需求将波形数据从EPROM调到HSRAM中,即波形数据的加载状况;数据加载结束后,依照DDS组成原理进行信号组成,即信号的组成状况。体系规划中运用单片机的P1口操控这两种作业状况之间的切换。

1、波形数据的加载

单片机体系上电自检结束后,开端进行波形数据加载进程。此刻,地址总线操控模块和数据总线操控模块,将总线的操控权交给单片机体系。在该进程中,EPROM处于读状况,而SRAM为写状况。8031 依照EPROM、SRAM的时序要求,将8 k的波形数据从EPROM加载到HSRAM中。该进程大约需求几毫秒时刻。

由此咱们知道,用这种办法不只可以组成规范波形(如:正弦波、方波、三角波等),并且还可以组成各种非规范波形。对此咱们只需经过数据收集器或PC机取得8 K的波形数据,然后存入到EPROM中,就可以按所需求的频率输出相应波形。

2、波形组成电路的规划

当波形数据加载结束后,体系就可以进行信号组成。单片机将接纳到的频率值转化成频率操控字,送到相位累加器。相位累加器在每一个时钟周期进行相位累加,然后将每次的累加和作为地址去寻址SRAM,读出与该地址所对应的波形起伏值,然后送到D/A转化器转化成模拟信号,最终经起伏扩大、滤波输出。

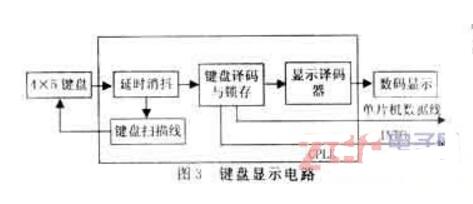

1) 频率值的接纳与显现

键盘、显现部分用来完成用户与单片机的交互。体系选用中止查询的办法接纳经过键盘输入的频率值。该频率值一方面送到数码显现接口进行显现,另一方面转化成频率操控字送往相位累加模块。键盘显现接口部分如图3所示,图中虚线框内部分均由CPLD完成。

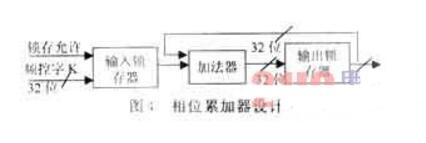

2)数控振动源(NCO)规划完成

这一部分是DDS信号组成中的要害部分,由DDS体系原理框图(图2)可知,这一部分首要是由相位累加器、地址总线操控器、数据总线操控器与SRAM组成。其间,除了SRAM外,其他3个模块都是在CPLD上完成。

相位累加器是整个DDS体系作业的要害,它规划的好坏直接影响到整个体系的功用和如图4所示,它实质上是1个带反应的32位加法器,功能。把输出数据作为另一路输入数据和从微处理器送来的频率操控字进行接连相加,发生有规则的32位相位地址码。规划中选用流水线技能完成32位加法器,经过在组合逻辑之间刺进触发器,下降了寄存器之间的传输延时,然后确保体系可以在较高的时钟速度下作业。

地址总线操控模块和数据总线操控模块是依据体系作业状况的不同,对体系的地址总线、数据总线以及操控线进行切换,这一部分的规划比较简单完成,这儿就不再赘述。

3)输出信号调度部分

这一部分是由D/A转化器、起伏扩大器和滤波器构成,其电路如图5所示。

DA器材选用的是AD公司的高速芯片9713B,该芯片的输入是12位的。起伏调度电路是由扩大器组成。这是1个电流反应的高速扩大电路。它把DA输出的电流转化成电压,经过反应电阻RFB的电流决议9617输出的起伏。RL和RFF起分流效果,约束用于I/V转化的电流,一起在9617内部供给一个输出电压起伏。流过R2的电流给9617 输出端供给一个直流偏置,调度R1的阻值可以调整偏置电流的巨细。整个扩大电路最大的起伏是±4.096 V。模拟输出的最终部分是滤波电路,滤波器的挑选首要取决与体系所要输出的波形。比如咱们在用DDS技能组成正弦信号时,可以选用椭圆滤波器滤波。

四、结语

与传统的频率组成办法比较,DDS组成办法具有频率切换快、频率分辨率高、相位改变接连等一系列杰出长处。运用单片机灵敏的操控能力以及杰出的人机对话功用与CPLD的高功能、高集成度相结合,可以打破传统规划中的许多规划瓶颈,使体系功能大起伏进步;一起,用这种办法完成的DDS电路具有很大灵敏性,它可以依据用户的需求规划,满意用户的特殊要求。因而,该体系具有很好的开发、运用远景。

一起,咱们也应该注意到因为DDS数字化完成的固有特色,像相位累加器的相位舍位、波形起伏量化和DAC器材非抱负特性,使得输出信号频谱杂散较大。当组成信号的输出频率比较高时,体现得尤为杰出,然后约束了输出信号的频率规模。对此,咱们一方面在规划进程中应尽量减小可以引起杂散的各种因素,别的更重要的是采纳一些便于CPLD完成而一起可以有用下降输出杂散的技能,如对DDS相位累加器的改善、ROM数据压缩、运用颤动注入技能等。然后使开宣布的DDS体系功能愈加优秀。