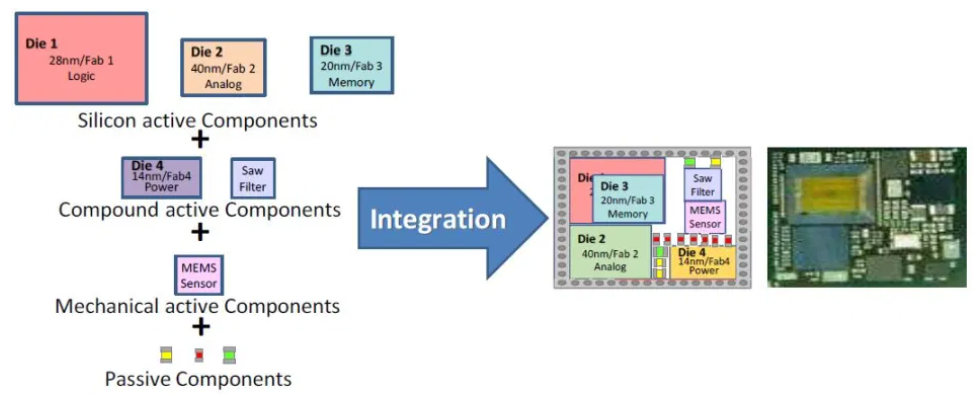

异构集成技能是指将独自制作的组件集成到更高等级的组件或体系封装(SiP)中,整体而言,该组件供给了增强的功用和改进的操作特性。

此外,这类组件可所以任何一种产品,例如微机电体系(MEMS)、高带宽存储器(HBM)的拼装封装(例如,无源元件)等(图1)。

图1异构集成技能怎么作业的高档视图。

不是摩尔规律的连续

严厉地说,摩尔规律是一种调查规律,它要求集成电路中晶体管的密度每两年翻一番。晶体管的集成密度在二维受到限制,这主要是因为栅极长度缩短的减缓,所以才开端运用三位技能。堆叠式内存作为3D晶片便是一个比如,多层相同技能的堆叠,添加了整合密度。

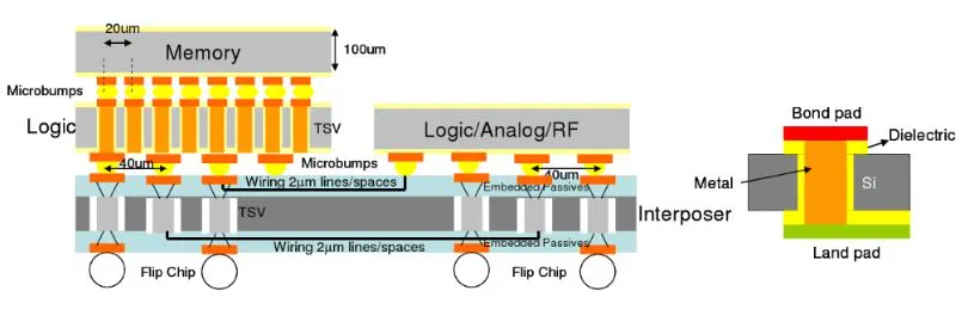

“逾越摩尔规律”指的是功用密度的添加,将多种技能集成到一个复合器材中。这或许包含芯片和/或封装的堆叠,运用多种半导体资料和各种电子布线技能,如球栅阵列(BGA)、硅通孔(TSV)、中间层和引线键合。一个逾越摩尔的器材可以经过异构集成将来自不同前端制作节点的逻辑、内存、传感器和天线集成到一个独自的封装中。

异构集成不是什么新鲜事

异构集成不是一个全新概念,多芯片组件(MCM)自20世纪70年代开端呈现,但是,先进的封装技能使电子封装制作业发生了革命性的改动。新的封装技能使来自不同制作工艺流程的芯片集成到具有多种功用的单个封装中。在曩昔的二十年里,这些封装技能的多样性在商场需求的推进下正在快速开展,经过更低的本钱取得更高的器材功用。

功耗、功用、面积和本钱(PPAC)是选用异构集成技能的要害驱动要素。更低的功耗、削减占用空间、更低的推迟、更高的速度和更高的带宽都能为顾客带来优势。

很自然地,扩展仍然是异构集成中的一个考量要素。互连、凸点封装、TSV和焊盘的缩放将有助于前进器材的PPAC。在这一进程中,先进的制程、东西以及办法学带来了更重要的应战。

光刻技能的改动

光刻也被逼习惯先进封装技能的开展。跟着设备的杂乱性不断开展,设备和封装规划的压力也越来越大,这就导致了许多协作开展机会。由此发生的技能创新需求设备、封装、体系规划师和制作商之间的联合,打破职业部分之间的前史边界。

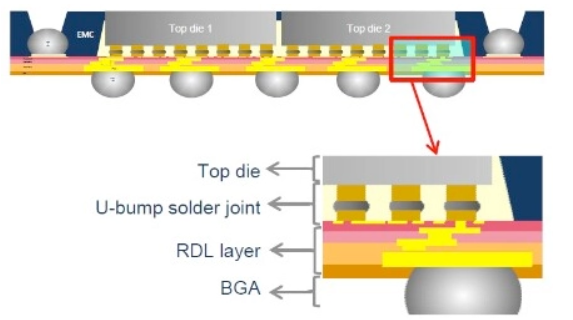

跟着异质结构的添加,器材、封装和PCB的交融也将添加,然后发生很多先进的封装处理计划,这些处理计划现已开展到合适特定体系的程度。例如,高功用核算(HPC)运用需求2.5D中间层技能来完成重布线层(RDL)。相比之下,顾客移动和物联网商场要求不那么严厉的规划规矩,不用选用贵重的中间层,而是挑选运用高密度扇出(HD-FO)封装技能将互连层嵌入到相关模具中。

中间层(TSV)和扇出(TSV-less)技能不是互斥的,可以组合在一个单一的混合技能封装中,终究很大程度上取决于器材的需求。

引线互联有两个计划。传统上,金属化互连被认为是一个BEOL范畴,但跟着2.5D和3D架构的呈现,这一边界变得含糊。对高功用互连的要求,要求笔直的衔接TSV或TMV,直接经过硅,弥补和替代传统的线衔接和倒装芯片处理计划,过孔技能已成为完成高功用互连的要害(图2)。

图2异构集成展现了TSV和中间层功用。

RDL和bumping应战

跟着互连技能的改动,出产它的光刻技能要求也随之改动。一些曾经的BEOL进程现在运用FEOL东西运转,而一些BEOL东西现在在运转BEOL晶圆时依照FEOL规范履行。一切的光刻工艺都着重特征分辨率、临界尺度(CD)操控和掩盖精度目标,一起坚持高出产率和低本钱。

因为分辨率的原因,通常在高数值孔径(NA)下操作的FEOL光刻东西现在的使命是精细线/空间、通孔和微凸图形,以完成初始互连界说。跟着互连层和再分配层的密度添加,与较厚的光刻胶膜、基板翘曲和聚集深度相关的应战变得杂乱,频频呈现在FEOL上的高钠光刻体系不再可以满意困难制程。

某些先进的封装技能选用更为困难的工艺流程,然后导致更难制作晶圆。例如,在无TSV重组eWLB或扇出型晶圆上的模具移位和晶圆描摹,这分别对高档封装光刻工艺流程中的掩盖和聚集深度形成应战。这是一个不同的光刻办法是需求的,运用BEOL光刻东西,现已开发了处理这些问题的有用且通用的处理计划。

其次,倒装芯片(bumping)是一个界说明确且安稳的进程,多年来一直是职业规范。虽然它也受到了扩展的影响,但bumping仍然是异构集成的高档打包的根底。一般来说,凸点光刻是用较厚的感光资料进行的,这些资料获益于具有低钠和高聚集深度的模具,以界说更大的倒装芯片。

这是一个多芯片的概念性完成,带有微凸点、铜柱和倒装芯片凸点,在这种情况下不需求TSV,运用Amkor的硅片集成扇出技能(SWIFT)。

但是,跟着职业细分的缩小,将FEOL和BEOL拉近,BEOL东西的灵活性变得至关重要。处理翘曲晶圆的才能、宽频曝光GHI、多膜堆的GH和I线波长,以及具有大深度聚集操控的分辨率习惯性的可变NA,这些都被证明对高出产率、高产值和杰出的本钱至关重要。

这种灵活性将是极其重要的,特别是外包半导体封装厂(OSAT)。与各种FEOL曝光场尺度、衬底尺度和资料类型相匹配的多功用性也是一个重要的考虑要素。前进精度以完成更严密的掩盖、更高的出产功率和更高的曝光均匀性以改进CD均匀性,这一要求将FEOL和BEOL东西功用结合起来,用于前沿的异质集成技能运用。

现代前沿运用,如人工智能(AI)、高功用核算机(HPC)、5G、物联网(IoT)和移动消费品,正以越来越低的本钱推进对电子设备功用的需求。异质集成技能使半导体器材制作商可以将来自不同制作工艺流程的功用部件组合成具有杂乱和先进功用的单一复合器材。

由这些技能发生的先进封装出产需求对光刻和弥补工艺提出了应战,要求它们以更高的规范履行,以支撑所需的互连和TSV处理层要求。在这里,设备本钱和因为杂乱性添加而下降的出产率或产值是制作商即将处理的应战。在产值和工艺流程的前进之前,高端运用将从异构集成中获益。