简介

大多数存储器接口都是源同步接口,从外部存储器器材传出的数据和时钟/ 选通脉冲是边缘对齐的。在 Virtex-4 器材收集这一数据,需求推迟时钟/ 选通脉冲或数据。运用直接时钟操控技能,数据经推迟,并与内部 FPGA 时钟完成中心对齐。在这个计划中,内部 FPGA时钟收集传出的数据。存储器传出的时钟/ 选通脉冲用于决议与数据位相关的推迟值。因而,与选通脉冲相关的数据位的数量不受约束。由于无需将选通脉冲分配给相关数据位,所以不需求其他时钟资源。

时钟/ 选通脉冲和数据位运用的 Virtex-4 资源是一条 64-tap 肯定推迟线。该 64-tap 肯定推迟线可运用 IDELAY 和 IDELAYCTRL primiTIve 完成。时钟/ 选通脉冲和数据位均经过此 64-tap肯定推迟线来布线。尽管选通脉冲不 用于收集数据,但它用于确认数据与内部 FPGA 时钟完成中心对齐所需的 tap 数量。以下部分将具体解说直接时钟操控技能计划的规划及完成。

选通脉冲边缘检测

与时钟/ 选通脉冲相关的数据位的推迟值便是内部 FPGA 时钟上升沿与时钟/ 选通脉冲中心之间的相位差。假定时钟/ 选通脉冲和数据完成了边缘对齐。要确认这个相位差,时钟/ 选通脉冲经过 IOB 内的 64-tap 肯定推迟线输入,并运用内部 FPGA 时钟在增量 tap 输出端对其进行采样。

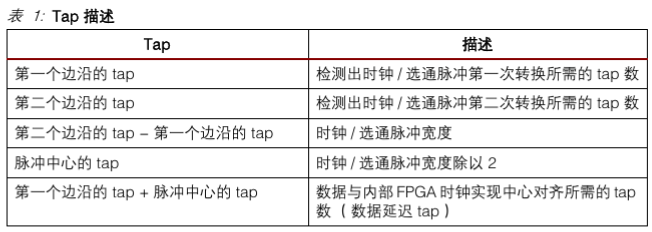

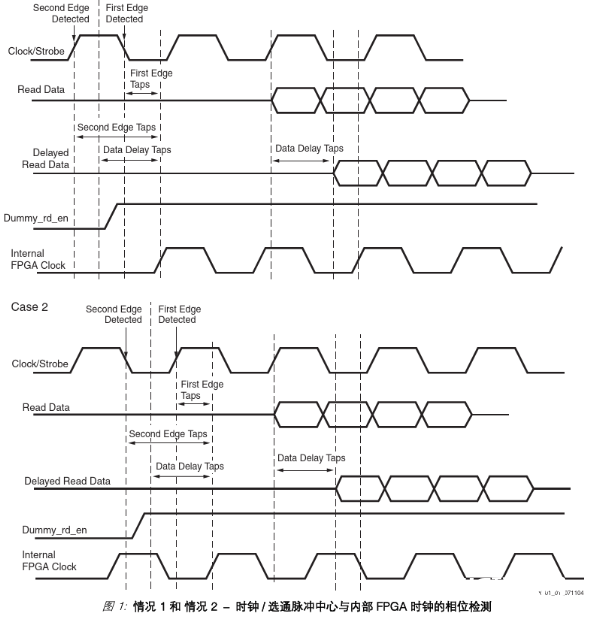

要确认时钟/ 选通脉冲的中心,至少需求检测到时钟/ 选通脉冲的两个边缘或转化。检测出第2次转化所需的 tap 数(即第二个边缘的 tap)和检测出第一次转化所需的 tap 数(即第一个边缘的 tap)之差,即为时钟/ 选通脉冲宽度。这个差值的二分之一便是脉冲中心(即脉冲中心的 tap)。从内部 FPGA 时钟上升沿到时钟/ 选通脉冲中心之间的 tap 数,即为第一个边缘的tap 数与脉冲中心的 tap 数之和。

图1 说明晰经过使数据推迟相应的 tap 数,让数据与内部 FPGA 时钟完成中心对齐的两种状况。第 1 种状况所示为,由于时钟/ 选通脉冲的下降沿是被检测到的第一个边缘,因而内部FPGA 时钟的上升沿坐落推迟数据的中心。第 2 种状况所示为,由于时钟/ 选通脉冲的上升沿是检测到的第一个边缘,因而内部 FPGA 时钟下降沿坐落推迟数据的中心。

完成选通脉冲边缘检测由于具有专用的 IDELAY 和 IDELAY_CTRL 电路,所以能够轻松地在 Virtex-4 器材中完成确认推迟值的电路。完成确认推迟值电路的结构图如图2 所示。

运用一个简略的算法检测存储器时钟/ 选通脉冲的边缘。将初始值为 0 的时钟/ 选通脉冲输入IDELAY 模块。时钟/ 选通脉冲将不停地添加 1 tap 的推迟,直到检测到第一个边缘。然后记载下检测出第一个边缘所需的 tap 数。在检测到第二个边缘之前,时钟/ 选通脉冲依然不停地添加 1 tap 的推迟。然后记载下检测出第二个边缘所需的 tap 数。依据两次记载的值,核算出脉冲宽度。在用 tap 数确认时钟/ 选通脉冲宽度后,除以 2 即得到中心值。中心值与检测出第一个边缘所需的 tap 数之和为推迟数据所需的tap 数。

IDELAY 模块可用的 tap 总数为64。因而,当频率为 200 MHz 或以下时,将无法检测出两个边缘。如果在 64 tap 完毕后仅检测出一个边缘,那么推迟数据所需的 tap 数应为,检测出第一个边缘所需的 tap 数减去 16 tap (约 1.25 ns,每个 tap 的延时约为 75 ps)。一个 200 MHz 时钟/ 选通脉冲周期的四分之一约为 16 tap。依据时序剖析,该值也适用于更低的频率,最低可达 110 MHz。当频率低于 110 MHz 时,如果在 64 tap 完毕后未检测出任何边缘,那么推迟数据所需的 tap 数应为 32 tap(约 2.5 ns,每个 tap 的延时约为 75 ps)。该值足以使内部 FPGA时钟边缘坐落数据窗口内。

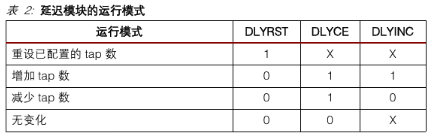

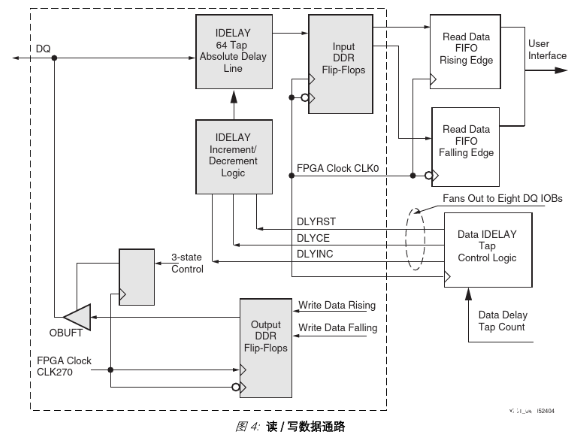

检测第一个和第二个边缘仅需一个小型状况机。只要在为确认数据推迟 tap 数而宣布的虚读操作过程中,才启用该状况机。在正式作业之前,发送至外部存储器器材的虚读操作指令包含多条背靠背读指令。状况机将操控输入 IDELAY 电路的信号,即DLYRST、DLYCE 和 DLYINC。

DLYRST - 推迟线复位信号,将推迟线中的 tap 数重设为按 IOBDELAY_VALUE 特点设置的值。本规划中被设为 “0”。

DLYCE - 推迟线使能信号,确认何时激活推迟线递加/ 递减信号。

DLYINC – 推迟线递加/ 递减信号,可添加或削减推迟模块中的 tap 数。表2 描绘了推迟线的运转形式。

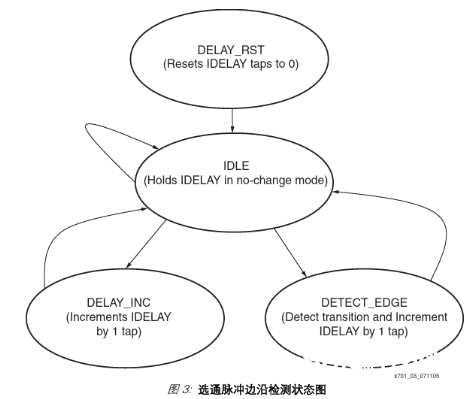

用于操控这些推迟模块输入的状况图如图3 所示。该状况机的四种状况分别为:DELAY_RST、IDLE、DELAY_INC 和 DETECT_EDGE。

DELAY_RST

该状况是建议虚读操作时启用的状况机的第一个状况。在这种状况下,推迟模块被重设为“0”tap。该状况之后是多个 IDLE 状况。

IDLE

在这种状况下,推迟模块坚持“无变化”运转形式。除 IDLE 状况之外,每种状况完毕后都会呈现数个 IDLE 状况, 以便处理 tap 输出值。IDLE 状况之后是另一个 IDLE、DELAY_INC 或DETECT_EDGE 状况。

DELAY_INC

这个状况使推迟模块tap 数加 1。该状况之后是数个IDLE 状况。

DETECT_EDGE

在这种状况下,比较推迟模块的输出及其上一个值,用于检测信号边缘或转化,一起,推迟模块tap 数加 1。该状况之后是数个 IDLE 状况。

在确认了推迟数据所需的 tap 数后,将启用数据 IDELAY 电路,并添加到这一数值。依照所需的 tap 数,使数据 IDELAY 电路添加相同的时钟周期。数据 IDELAY 电路的读/ 写数据通路结构图如图4 所示。

数据收集与二次收集

如图4 所示,运用内部FPGA时钟,在输入 DDR 触发器中收集推迟数据。然后,把这些触发器的输出存储到两个FIFO 中;一个代表上升沿数据,另一个代表下降沿数据。这些FIFO 是运用LUT RAM 完成的,其写使能操作由操控器生成的读使能信号供给,并在数据格式校准的基础上与收集的读取数据对齐。

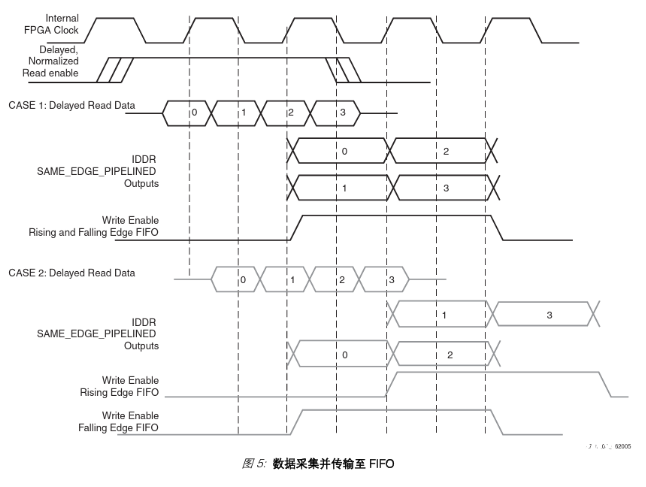

DDR2 SDRAM 器材并未随读取数据一起供给读有用或读使能信号。因而,操控器将依据 CAS推迟和突发长度,生成这个读使能信号。在开端履行读取操作时,有必要令该读使能信号有用,并在选通脉冲的终究一个上升沿完毕后使其无效。在IDDR 触发器的输出端,该读使能信号有必要与收集到的读取数据对齐。为了完成读使能对齐,在数据与FPGA 时钟对齐后,将已知数据格式写入存储器。然后读回已知数据格式,并在读使能信号与收集到的读取数据对齐之前,运用移位寄存器推迟读使能信号。每字节数据都会生成一个读使能信号。图5 为读使能对齐的时序图。

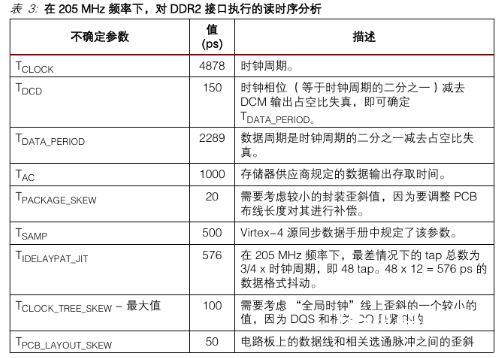

读时序剖析

这一部分介绍了运用直接时钟操控技能完成的读时序剖析。直接在FPGA 时钟域内收集读取数据,因而,用于数据有用窗口剖析的存储器参数便是存取时刻 (TAC)。下面扼要介绍了此时序剖析中运用的各个参数。

此时序剖析中考虑的外部存储器参数有:

TAC – 读取数据 (DQ) 的存取时刻(以FPGA 传递给存储器的时钟为参照)

TDCD – DCM 输出占空比失真

运用FPGA 时钟而非存储器时钟/ 选通脉冲(DQS),来收集读取数据(DQ) ;因而,该剖析考虑了TAC (以时钟为参照的数据存取时刻)。在此剖析中,未考虑DQS – DQ 存储器参数,如TDQSQ 和TQHS,由于 TAC 比这两个参数更重要。

此时序剖析中考虑的FPGA 参数有:

TCLOCK_TREE-SKEW – 严密放置在该组中的 IOB 触发器的大局时钟树倾斜

TPACKAGE_SKEW – 特定器材/ 封装的封装

倾斜

TSAMP – Virtex-4 源同步数据手册中规则的采样窗口

TIDELAYPAT_JIT – Virtex-4 数据手册中规则的每个 IDELAY tap 的数据格式颤动

经过检测 DQS 边缘,核算出与 DQS 相关的数据位推迟。运用大局时钟在 I/O 触发器中收集DQS 来进行检测。因而,终究得到的数据推迟值现已包含了 I/O 触发器的树立时刻和坚持时刻。在进行最差状况剖析时,需求考虑 I/O 触发器固有的树立时刻和坚持时刻。

此外,核算数据位和相关选通脉冲之间的倾斜也需求考虑 PCB 布局倾斜。

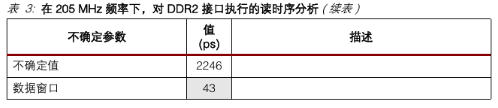

表3 所示为在205 MHz 频率下,对DDR2 接口履行的读时序剖析。悉数参数单位均为皮秒。

TDATA_PERIOD 是时钟周期的二分之一减去TMEM_DCD。TDATA_PERIOD 与不确认值之和的差,便是有用数据窗口 (43 ps)。因而,在 205 MHz 频率下,-11Virtex-4 器材将发生 43 ps 的余量。

参阅规划

存储器接口生成器 (MIG) 东西中集成了直接时钟操控数据收集技能的参阅规划。该东西已被集成到 Xilinx Core Generator 东西中。最新版参阅规划,可从 Xilinx 网站下载 IP 更新:http://www.xilinx.com/cn/xlnx/xil_sw_updates_home.jsp

定论

Virtex-4 I/O 架构增强了源同步存储器接口的完成。本运用攻略及参阅规划中运用的架构特性包含:

IDELAY 模块 – 接连校准的 tap 延时很小的推迟元件。

FIFO16 primiTIve – 用作 FIFO 的 Block RAM,无需运用生成状况标志所需的其他 CLB 资源。

高速差分大局时钟资源供给了更好的占空比。差分时钟削减了参阅规划所需的大局时钟资源数量。

责任编辑:gt