平常没留意单片机的I/0结构,认为软件置0的端口,加个外部高电平就能够拉高,下次采样的时分,就成了高电平了。现在看了一下P口结构才知道,不可。

P0口做通信誉,输出用时,有必要外部加上拉电阻,拉高到电源,否则会犯错!!!!!

内部把端口置0之后,场效应管导通到地,把电平拉到了地。就算外部加一个高电平信号,由于此刻引脚相当于对地短接,所以引脚状况仍是低电平。

可是:假如外部加一个电流很大的高电平信号,仍是能够把引脚电平拉高的。由于内部场效应管有必定内阻。可是留意用是不允许的。会缩短单片机寿数。

所以:单片机采样引脚外部电平信号时,一般要内部把引脚举高,采样外部拉低信号。假如非要采样外部引脚高电平的信号。那有必要初始状况引脚为低电平,而内部又不能置低。解决办法是:引脚接一个电阻到到地,外部没有高信号来时,引脚被“外部拉低”,来高电平信号时,才“外部举高”引脚。

一、P0端口的结构及作业原理

P0端口8位中的一位结构图见下图:

由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。再看图的右边,标号为P0.X引脚的图标,也便是说P0.X引脚能够是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,咱们先就组成P0口的每个单元部份跟咱们介绍一下:

先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,咱们已知道,三态门有三个状况,即在其的输出端能够是高电平、低电平,一起还有一种便是高阻状况(或称为禁止状况),咱们看上图,上面一个是读锁存器的缓冲器,也便是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态操控端(上图中标号为‘读锁存器’端)有用。下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的操控端有用,引脚上的数据才会传输到咱们单片机的内部数据总线上。

D锁存器:构成一个锁存器,一般要用一个时序电路,时序的单元电路在学数字电路时咱们已知道,一个触发器能够保存一位的二进制数(即具有坚持功用),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。咱们看上图中的D锁存器,D端是数据输入端,CP是操控端(也便是时序操控信号输入端),Q是输出端,Q非是反向输出端。

关于D触发器来讲,当D输入端有一个输入信号,假如这时操控端CP没有信号(也便是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。假如时序操控端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。数据传送过来后,当CP时序操控端的时序信号消失了,这时,输出端还会坚持着前次输入端D的数据(即把前次的数据锁存起来了)。假如下一个时序操控脉冲信号来了,这时D端的数据才再次传送到Q端,然后改动Q端的状况。

多路开关:在51单片机中,当内部的存储器够用(也便是不需求外扩展存储器时,这儿讲的存储器包含数据存储器及程序存储器)时,P0口能够作为通用的输入输出端口(即I/O)运用,关于8031(内部没有ROM)的单片机或许编写的程序超过了单片机内部的存储器容量,需求外扩存储器时,P0口就作为‘地址/数据’总线运用。那么这个多路挑选开关便是用于挑选是做为一般I/O口运用仍是作为‘数据/地址’总线运用的挑选开关了。咱们看上图,当多路开关与下面接通时,P0口是作为一般的I/O口运用的,当多路开关是与上面接通时,P0口是作为‘地址/数据’总线运用的。

输出驱动部份:从上图中咱们已看出,P0口的输出是由两个MOS管组成的推拉式结构,也便是说,这两个MOS管一次只能导通一个,当V1导通时,V2就截止,当V2导通时,V1截止。

与门、与非门:这两个单元电路的逻辑原理咱们在第四课数字及常用逻辑电路时已做过介绍,不明白的同学请回到第四节去看看。

前面咱们已将P0口的各单元部件进行了一个具体的解说,下面咱们就来研究一下P0口做为I/O口及地址/数据总线运用时的具体作业进程。

1、作为I/O端口运用时的作业原理

P0口作为I/O端口运用时,多路开关的操控信号为0(低电平),看上图中的线线部份,多路开关的操控信号一起与与门的一个输入端是相接的,咱们知道与门的逻辑特点是“全1出1,有0出0”那么操控信号是0的话,这时与门输出的也是一个0(低电平),与让的输出是0,V1管就截止,在多路操控开关的操控信号是0(低电平)时,多路开关是与锁存器的Q非端相接的(即P0口作为I/O口线运用)。

P0口用作I/O口线,其由数据总线向引脚输出(即输出状况Output)的作业进程:当写锁存器信号CP 有用,数据总线的信号→锁存器的输入端D→锁存器的反向输出Q非端→多路开关→V2管的栅极→V2的漏极到输出端P0.X。前面咱们已讲了,当多路开关的操控信号为低电平0时,与门输出为低电平,V1管是截止的,所以作为输出口时,P0是漏极开路输出,类似于OC门,当驱动上接电流负载时,需求外接上拉电阻。

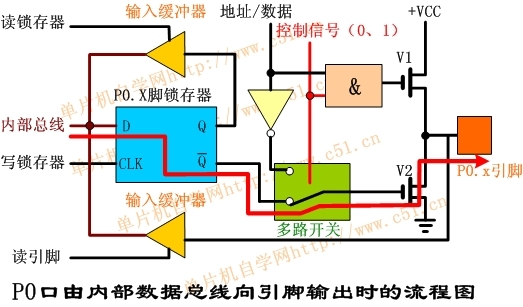

下图便是由内部数据总线向P0口输出数据的流程图(赤色箭头)。

数据输入时(读P0口)有两种状况

1、读引脚

读芯片引脚上的数据,读引脚数时,读引脚缓冲器翻开(即三态缓冲器的操控端要有用),经过内部数据总线输入,请看下图(赤色简头)。

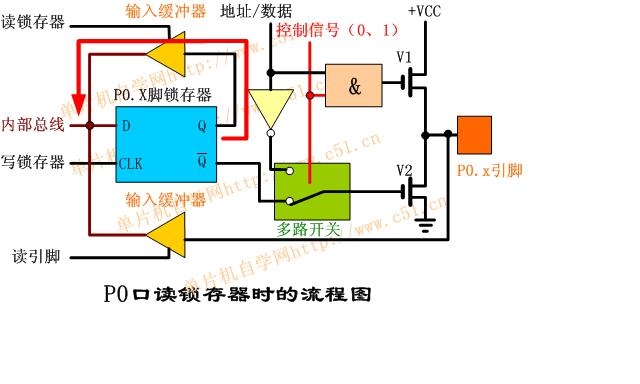

经过翻开读锁存器三态缓冲器读取锁存器输出端Q的状况,请看下图(赤色箭头):

在输入状况下,从锁存器和从引脚上读来的信号一般是共同的,但也有破例。例如,当从内部总线输出低电平后,锁存器Q=0,Q非=1,场效应管T2注册,端口线呈低电平状况。此刻不管端口线上外接的信号是低电乎仍是高电平,从引脚读入单片机的信号都是低电平,因此不能正确地读入端口引脚上的信号。又如,当从内部总线输出高电平后,锁存器Q=1,Q非=0,场效应管T2截止。如外接引脚信号为低电平,从引脚上读入的信号就与从锁存器读入的信号不同。为此,8031单片机在对端口P0一P3的输入操作上,有如下约好:为此,8051单片机在对端口P0一P3的输入操作上,有如下约好:凡归于读-修正-写方法的指令,从锁存器读入信号,其它指令则从端口引脚线上读入信号。