摘要:为了满意高速图画数据收集体系中对高带宽和大容量的要求,运用Virtex-7 系列FPGA 外接DDR3 SDRAM 的规划办法,提出了一种依据Verilog-HDL 言语的DDR3 SDRAM 操控器用户接口规划计划。该操控器用户接口现已在Xilinx 公司的VC707 开发板上经过了功用验证,并成功的被使用到高速图画数据收集体系中。含有该用户接口的操控器具有比一般的操控器接口带宽运用率高、可移植性强和本钱低的长处,可以依据规划人员的需求被灵敏地使用到不同的工程。

跟着现代科学技能的高速开展,在工业生产和科学研究上,如卫星通信、高速图画处理等范畴,普遍存在对数据进行高速大容量、实时性强和高带宽的处理要求[1,2]。高速数据收集体系作为各个体系中比较中心的部分,对数据处理的速度、实时性、稳定性以及功耗等要求都越来越高。

现在,在可以一起满意高带宽和大容量要求的存储器计划中,比较老练的有DDR,DDR2,DDR3等,其间DDR3 具有更高的带宽和更低的功耗,因而成为高速实时数据存储体系规划中的首选计划[3]。由于DDR3 内存不可以直接辨认处理器的拜访恳求,所以有必要经过规划一款操控器去操控DDR3的正常读写操作。

Virtex-7 系列FPGA 与Virtex-6 系列FPGA 比较,体系功用提高了一倍,功耗下降了一半,存储器带宽提升了2 倍,而且内有共同的IP核mig_v1. 7,可用来处理运用DDR3 存储器时的一些复杂问题。因而本文在介绍DDR3 的作业原理的基础上,结合IP 核MIG_v1. 7,给出了一种运用Verilog-HDL 言语规划DDR3-SDRAM 操控器用户接口的办法,而且提出了一种在高速图画数据收集体系中DDR3 存储器的使用计划,一起在Virtex-7 系列的FPGA 上完结。

1 DDR3-SDRAM 的技能特色

本文选用的DDR3-SDRAM 为Micron 公司的MT8JTF12864HZ-1G6G1 内存条。该DDR3 内存条的存储空间为1 GB,由8 片容量为128 MB 的内存芯片构成。每个芯片的数据位宽为8 位,行地址线复用14 根,列地址线复用10 根,Bank 数量为8 个,因而每个内存芯片的容量为16 384 mes; 1 024 mes; 8 mes; 8,即128 MB。8 片组成在一起就构成了MT8JTF12864HZ-1G6G1 的64 位数据位宽,容量为1 GB。

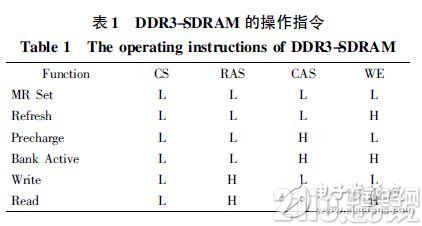

DDR3 的操控指令信号首要有芯片挑选信号CS、行地址挑选信号RAS、列地址挑选信号CAS 和WE 写使能信号,DDR3 的各种操作指令实质上都是经过这四个信号的组合决议的,如表1 所示。其间H 表明高电平,L 表明低电平。

表1 DDR3-SDRAM 的操作指令

DDR3 的Mode Register 有四个,分别为MR0、MR1、MR2 和MR3,当四个操控指令信号均为低电平时,即可经过Bank 挑选位对方式寄存器进行挑选; Refresh 操作分为Auto Refresh 与Self Refresh 两种,其间不论是何种Refresh 办法,都不需求外部供给行地址信息,由于这是一个内部的主动操作;DDR3 在进行读写操作时,内存会给出一个与数据同步的DQS 信号,用来在一个时钟周期内精确区域分出每个传输周期,提高了接纳方接纳数据的精确度。

与上一代存储器材比较,DDR3 的内存方式有了很大的改善: 逻辑Bank 数量由DDR2 的4 个增加为8 个; 突发长度增加为8 bit,任何突发中止操作都将在DDR3 内存中予以制止,且不予支撑; 取而代之的是更为灵敏的突发传输操控; 其间心作业电压由DDR2 的1. 8 V 降至1. 5 V[4],可以在到达高带宽的一起,大幅度的下降其功耗; DDR3 选用FLY_BY 总线,参阅电压别离,增加了ZQ 校准功用,然后大大的提高了存储信号的完好性; 而且DDR3 为绿色封装,不含任何有害物质,减少了对空气的污染。

2 DDR3-SDRAM操控器用户接口的规划

DDR3 操控器的规划选用了Xilinx 推出的IP 核MIG_v1. 7 + 用户接口模块的规划办法,其间本次规划首要是对用户接口模块进行论述。图1 为DDR3操控器的整体完结计划。

图1 DDR3 操控器的整体完结计划

2. 1 用户接口模块的规划

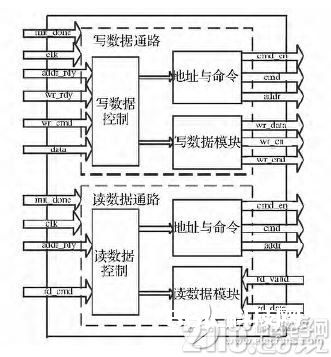

用户接口模块为整个DDR3 操控器体系的中心模块,其间首要包含写数据通路和读数据通路两个部分,图2 为DDR3 操控器的用户接口规划的完结计划。

图2 DDR3 操控器的用户接口规划

在写数据通路的输入端,addr _ rdy、wr _ rdy 和init_done 为DDR3 IP 核反应给写数据操控模块的信号, init_done 为高电平时指DDR3 现已完结初始化操作,addr_rdy 为高电平时表明DDR3 准备好接纳写数据地址和写数据指令,wr_rdy 为高电平时表明DDR3 准备好接纳写数据; wr_cmd 为写数据指令信号。在写数据通路的输出端,cmd_en 为输入到DDR3 IP 核的指令和地址的使能信号,wr_en 和wr_end 为输入到DDR3 IP 核的写数据操控信号,跟有用写数据信号对齐。

在用户接口的规划中选用back_to_back 的读写规划方式,将addr_rdy、cmd_en、cmd 和addr 作为地址总线,将wr_rdy、wr_en、wr_end 和wr_data 作为数据总线,两条总线是彼此独立的,两个反应信号addr_rdy 和wr_rdy 也是相对独立的。在写数据开端的时分,要保证地址总线提早数据总线一个周期使能,在addr_rdy 和wr_rdy 没有反压的抱负情况下,写数据要比写地址和写指令推延一个周期宣布,当addr_rdy 和wr_rdy 有反压时,写数据和写地址可以不满意相差一个周期被宣布的。

读数据通路与写数据通路的规划原理类似,其间rd_valid 为读数据有用信号, rd_data 为读数据信号。在读数据通路中将addr_rdy、cmd_en、cmd 和addr 作为地址总线,rd_valid 和rd_data 作为读数据总线。

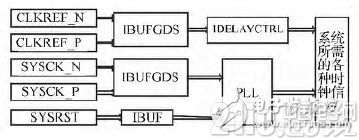

2. 2 用户接口的时钟模块规划

从外界输入200 MHz 的推迟参阅时钟、200MHz 的差分输入时钟,这些输入信号经过时钟和体系复位模块后可以生成整个DDR3 操控器和DDR3作业的悉数时钟,包含用户接口的作业时钟、DDR3 IP 核的作业时钟和DDR3 读写数据的时钟等。这种规划办法,具有简化操控器的规划结构,便于对时钟进行办理的长处[5]。图3 为时钟模块的完结模型。

图3 时钟和体系复位模块

3 DDR3-SDRAM操控器用户接口的仿真

DDR3-SDRAM 的作业有必要依照必定的规矩进行,有必要契合相应的状况机转化要求,图4 给出了DDR3 存储器作业的状况机,该状况机描绘了DDR3各个状况的转化以及转化时所触及的一些指令。DDR3 操控器的规划实质上是围绕着该状况机的进行规划的,以保证内存模块上的每个DDR3 都能正常的进行作业。

图4 DDR3 存储器的状况机

3. 1 用户接口规划模块的Chipscope 仿真成果剖析

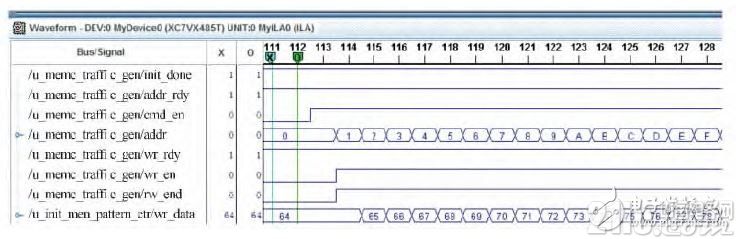

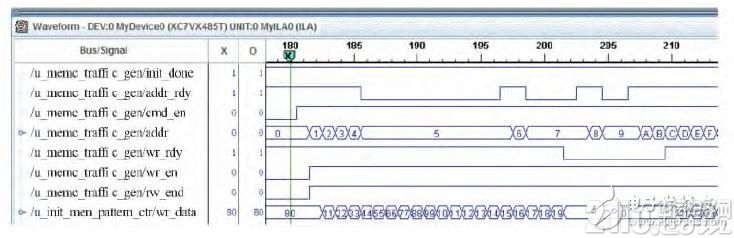

在本次规划中,硬件仿真选用将含有此用户接口模块的操控器下载到Virtex-7 系列FPGA 上,经过Chipscope 在线实时地调查用户接口内部的信号。和图6 中addr 每隔一个时钟周期加1 的现象。

3. 2 用户接口规划模块的Modelsim 仿真成果剖析

在本次规划中,软件仿真选用ISE 14. 3 与Modelsim10.0a 相结合的办法。

图5 为在抱负情况下,用户接口的输入信号addr_rdy 和wr_rdy 在无反压时分的内部信号观测图,在此状况下,cmd_en 比wr_en 和wr_end 提早一个周期被拉高,有用地址与相应的有用数据之间一向保持着一个周期的时刻推迟。图6 为用户接口在addr_rdy 和wr_rdy 信号有反压情况下的内部信号观测图,在此状况下,初始时刻cmd_en 比wr_en 和wr_end 提早一个周期被拉高,有用地址与相应的有用数据之间相差一个周期的时刻推迟,可是跟着addr_rdy 和wr_rdy 被拉低之后,有用地址与相应的有用数据之间不再满意相差一个周期的时刻推迟。由于在本次规划中选用的是back-to-back 方式,地址总线与数据总线彼此独立,所以即便有用地址与相应的有用数据之间不再满意相差一个周期的时刻推迟,也不会影响数据的传输。在此方式下,数据与地址的传输比较灵敏,操控起来比较便利,也有用的避免了数据的丢掉。

图5 addr_rdy 信号和wr_rdy 信号无反压的内部信号观测图

图6 addr_rdy 信号和wr_rdy 信号有反压的内部信号观测图

图7 写数据的Modelsim 仿真图

由于DDR3 选用的突发传输长度BL = 8,读写地址值以8 为单位接连增加,这样addr 的低3 位将一向为0,所以在运用Chipscope 对地址进行观测时,是从addr 的第4 位开端观测的,即呈现图5。

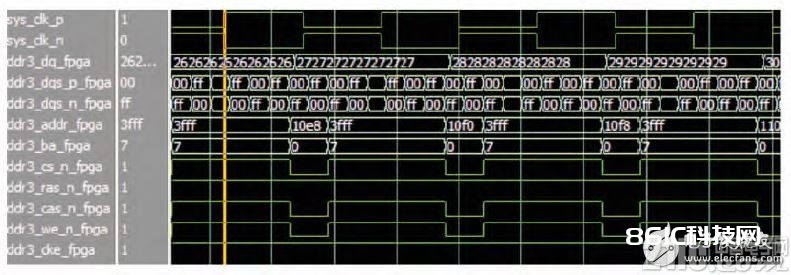

由于此次规划选用的内存中心频率为200MHz,又由于选用的DDR3 的内存总线位数为64位,DDR3 一次可以预读取8 位,依据内存带宽= 内存中心频率mes; 内存总线位数× 倍增系数,所以在不考虑刷新和激活等操作所占用的带宽下,DDR3 的内存带宽可以到达12. 5 GB,传输速率可到达1 600MB /s。在如此快的传输速率下,运用Chipscope 难以观测由DDR3 操控器写入到DDR3 内部的数据。所以在本次规划中,选用在ISE14. 3 里边临DDR3操控器的工程增加DDR3 模型,运用Modelsim 对DDR3 操控器和DDR3 模型进行联合仿真的办法对由操控器写入到DDR3 内部的数据进行观测。

从图7 中可以看出,在一个时钟周期内dq 的同步信号qds_n 和dqs_p 变化了8 次,也就是说,在一个时钟周期内写数据以64 bit 为单位被写入了8次。由用户接口传输过来的数据经过DDR3 IP 核之后,可以精确的被写入到DDR3 里边。当进行读数据的时分,也是以64 bit 为单位,在一个时钟周期内读8 个64 bit 的数据。

3. 3 DDR3 操控器用户接口在高速图画数据收集体系中的使用

含有该用户接口的DDR3 操控器现已成功的被使用到某高速图画数据收集体系中,图8 为该高速图画数据收集体系收集到的图片。

图8 高速图画数据收集成果图

该图画收集体系设置CMOS 相机作业在选用8bit 位宽的双通道方式下,帧频为250 帧/s,其分辨率为2 040 × 1 024。收集体系将接纳到的图画数据经过DDR3 缓存之后,经过千兆以太网接口传输至PC 机,再将写入PC 机内的数据以图片的方式显示出来。图8 为收集体系接连收集到的两帧图片,从图中可以看出两帧图片的时刻距离为4 ms,满意帧数要求,而且图画明晰完好,到达了预期的规范。

4 定论

本次规划的硬件渠道为Xilinx 公司的Virtex-7 FPGA VC707 评价套件。7 系列的FPGA 具有比6系列和5 系列的FPGA 尺度小、本钱低、高性价比和大容量以及超高端衔接带宽等长处。

该内存操控器的用户接口规划可以对DDR3 内存模块进行很好的办理,一起完结用户发送的各种恳求,而且最大极限的提高了拜访内存的速度和带宽,避免了数据的丢掉,并成功的使用到某高速图画收集体系中。在此用户接口的基础上规划的内存操控器可以与市场上大多数干流内存进行兼容,可移植性强,大大下降了开发本钱。