CPU的主频高达几个GHz,FPGA的速率往往在几百兆。可是,往往咱们会说FPGA会给CPU进行加快。

尽管CPU主频很高,但其是通用处理器,做某个特定运算(如信号处理,图画处理)或许需求许多个时钟周期;而FPGA能够通过编程重组电路,直接生成专用电路,加上电路并行性,或许做这个特定运算只需求一个时钟周期。

假定咱们用FPGA完好的完结了CPU,然后再跑软件的话,确实比CPU慢。问题是FPGA不会那么干,它会直指问题实质,解决问题。

即便咱们用FPGA完结一个CPU,也是为了做一些芯片验证或许说需求一些需求CPU和FPGA需求紧密结合的场景,这种场景现在也逐渐由SoC的FPGA完结了。

举个详细的比方,比方有两个数组,其间有256个32位数,咱们现在要把它们对应相加变成一个数组,用CPU写最快大概是这姿态的:

r[0] = a[0] + b[0];

r[1] = a[1] + b[1];

…

r[255] = a[255] + b[255];

当然也或许会这么写(在分支猜测精确,指令缓存不大的状况下或许更快):

for (int i = 0; i < 255; i++)

r[i] = a[i] + b[i];

CPU指令流水线

依据之前描绘的根底,指令进入流水线,通过流水线处理,从流水线出来的进程,关于咱们程序员来说,是比较直观的。

I486具有五级流水线。分别是:取指(Fetch),译码(D1, main decode),转址(D2, translate),履行(EX, execute),写回(WB)。某个指令能够在流水线的任何一级。

流水线的数量不或许无限制添加,流水线的加快也有许多危险。即便流水线能够无限制添加,不论CPU的流水线又多少条,每个指令履行都有必要次序履行。对速率的提高也是有限的。

关于上图中的流水线有一个显着的缺点。关于下面的指令代码,它们的功用是将两个变量的内容进行交流。

第二条xor指令需求第一条xor指令核算的成果a,可是直到第一条指令履行完结才会写回。所以流水线的其他指令就会在当时流水级等候直到第一条指令的履行和写回阶段完结。第二条指令会等候第一条指令完结才干进入流水线下一级,相同第三条指令也要等候第二条指令完结。

这个现象被称为流水线堵塞或许流水线气泡。

对FPGA来说,也能够用上面相同的写法,不同在于:

CPU是一个一个加法核算,而FPGA排好逻辑电路,在一个时钟周期内核算结束。就算CPU主频比FPGA快100倍也赶不上啊。

核算机最基本的功用便是运算了,其间最基本的又要属加法运算。咱们知道核算机运用二进制来保存和处理数据,因而这儿的加减法运算都是用二进制进行。下面雅乐网总结了一些运算器中加法器的规划。

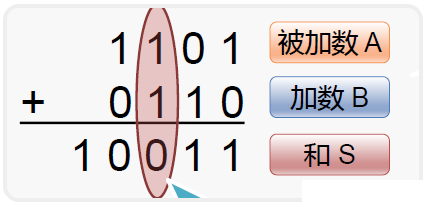

二进制加法

一位的二进制加法十分简略,因为只需四种状况

0+0=0 进位0

0+1=1 进位0

1+0=1 进位0

1+1=0 进位1

多位的二进制加法 和十进制相似,每一位上两个数相加后再加上进位就能够了

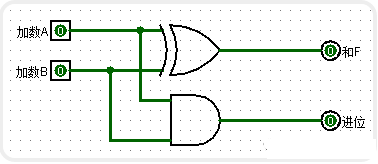

FPGA半加器

半加器能够完结两个1位的二进制数字相加,并且输出成果和进位。

真值表:

一位半加器真值表

由表中能够看见,这种加法没有考虑低位来的进位,所以称为半加。

输出和:A和B一个为0 一个为1的时分输出1 两个0或两个1输出0 因而 能够用异或门衔接。

进位:只需AB均为1的时分进位输出1 进位Cout = AB 用与门衔接。

一位半加器

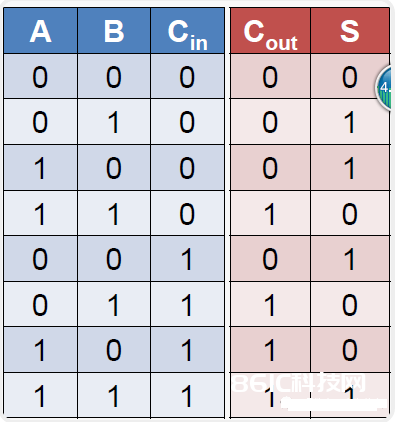

FPGA全加器

全加器在半加器的根底上 添加了进位 它输入三个数字 两个加数 和 一个进位 Cin,输出成果 和 进位

一位全加器真值表

从真值表很简单写出如下逻辑表达式

S=P异或Cout 其间P=A异或B

Cout=P·Cin+G 其间G=A·B

一位全加器

四位行波加法器

将四个全加器 每一个的仅为输出衔接到下一个的进位输入 就能够构成一个4位串行加法器了

四位行波加法器

这样构成的加法器衔接起来很简略,可是也有缺乏:每一个全加器核算的时分有必要等候它的进位输入发生后才干核算,所以四个全加器并不是一同进行核算的,而是一个一个的串行核算。这样会形成较大的推迟。

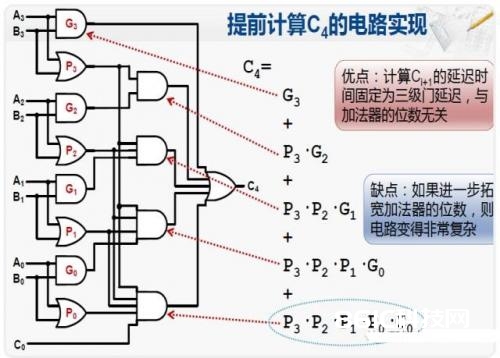

超前进位加法器(Carry-Lookahead Adder,CLA)

超前进位加法器的思路是提早算出每一位上的进位。

剖析每一个全加器的部分

一个全加器 A B Cn 假如有两个或两个以上的1 那么进位Cn+1便是1

因而 Cn+1 = AB + ACn + BCn = AB + Cn(A+B)

记生成(Generate)信号:Gi=Ai·Bi

传达(Propagate)信号:Pi=Ai+Bi

那么Ci+1=Gi+Pi·Ci

依据这个递推联系,能够推导出每一位的进位

每一位的进位跟前一级进位有关,前一级 又跟 前一级的前一级有关 一向向前 最终是和C0相关。而最开端的第一位C0和A0 B0都是已知的

这样算出成果只需求通过三个门推迟就能够了。

跟着位数的添加,进位的核算公式会越来越杂乱。32位的进位核算需求32与门

所以咱们需求更多的核算位宽或许更大的数组,或许矩阵的运算的时分,咱们运用FPGA的优势就表现出来。再多的核算,也便是放置更多的逻辑资源。

FPGA的并行是真并行,CPU彻底没得比。CPU假如想并行最多也便是让多个核并行,可是关于大部分算法完结来说,如上例,多个核之间的同步调度开支远远大于核算开支,就算多个核之间的调用开支能够做的很小,一般CPU也就那几个核,而FPGA只需门满足,想并行几路就能够并行几路。

所以在做可并行的核算密集型使命时,比方信号处理,网络传输等等FPGA能够帮上忙;可是假如做咱们常见的串行为主的使命而言,FPGA确实远远比不上CPU。

FPGA是副角

运用FPGA不必定总能加快,仅仅在某些强核算和数据处理的方面,因为其硬件电路并行运转和有许多DSP硬核资源供调用的特色,能够作业得更超卓。FPGA自身也仅仅辅佐人物,起操控的仍是CPU自身,所以FPGA并不能替代CPU,仅仅在完结一件大使命的进程中将某部分使命分化给FPGA能够更好地一同完结使命。在这进程中也会有额定的开支发生,在某些场合,或许用了FPGA而作用更差也是有的。

别的,一般说的运用FPGA加快比CPU和GPU省电,是指在完结相同的使命下,FPGA消耗的电力比起CPU和GPU更少一些,相对而言的,并不是说FPGA自身就必定省电。

FPGA的缺点

1.开发周期长。需求对特定的使用编写特定的FPGA。只需干的事情稍有不同,一般来说FPGA代码就要从头写一遍或许是至少要修正许多东西。开发价值和码农码几行代码彻底不可比。并且一般需求若干工程师花费若干周才干搞的定。重点是会写的人还不多。

2.并不是一切东西都合适FPGA。FPGA合适于做那些可并行核算的东西,例如矩阵运算。假如是一些判别类的问题,FPGA算得并没有CPU快(这个时分时钟周期才是关键因素)。所以实践中都是有人来剖析,在整个使命中有哪些当地能够并行核算,把这些当地替换为FPGA卡。

因为现在机器学习、大数据比较火,里边矩阵运算不计其数,所以没有呈现定制的AS%&&&&&%之前,FPGA加快仍是业界干流。现在百度、微软、谷歌等公司都现已把FPGA加快运用到了实践的商业运营中。