简介

精细模数转化器(ADC)的每秒采样数具有清晰界说且经过测验,精细数模转化器(DAC)则否则,其数据手册中并未对此加以界说,因为DAC的每秒采样数取决于许多要素。

大都状况下,DAC数字接口支撑高达50 MHz的时钟速率,假定输入移位寄存器为24位,则每秒能够履行2,000,000次写操作。但是,此数值仅表明数字接口承受新DAC码的才能,没有考虑数字处理推迟、时延以及模仿模块守时。

假如DAC无任何内部校准程序,则推迟能够疏忽,一般在数ns左右。假如DAC包含校准例行程序,则推迟或许在1 μs到3 μs左右。

就模仿模块而言,有两种不同状况与新码更新相关:

• 更新速度受与DAC相连的有源级的带宽约束,有源级一般是缓冲器,能够坐落内部或外部。

• 更新速度不受有源级约束,但受DAC内核约束。

关于第一种状况,树立时刻标准能够很好地用以估量模仿模块的才能。树立时刻界说新码与前码的联系,一般是¼到¾份额,在规则容差之内约为终究码的1 LSB左右。

关于大步进的码跃迁,压摆率是树立时刻的首要影响要素。此外,树立时刻还或许因为输出负载的虚部而添加,这与电容或电感类似,发生过冲或响铃振动。

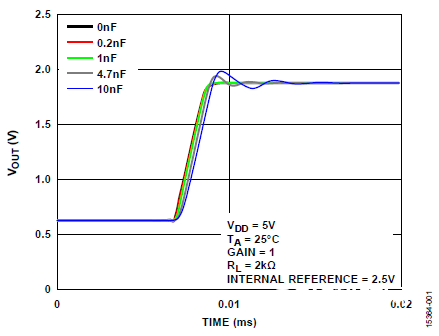

外部衔接的虚阻抗值决议过冲起伏,然后影响树立时刻,如图1所示。

图1.不同容性负载下VOUT与时刻的联系

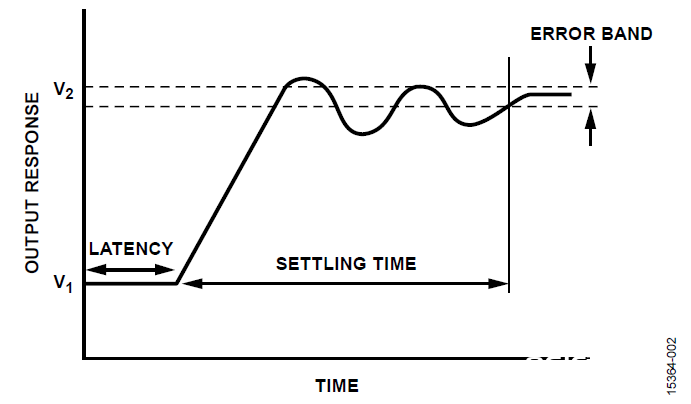

终究树立时刻是推迟、压摆率和响铃振动时刻一起影响的成果,如图2所示。

图2.终究树立时刻

所需的码步进越小,衔接的电容越低,则终究树立时刻越快。

当新码接近前码时,树立时刻或缓冲器才能不是约束性的;能够把这视为微调更新。

这种状况下,DAC内核的时延和动态效应是约束输出树立到规则容差范围内(即终究码的1 LSB左右)所需时刻的首要要素。

DAC在作业时会发生动态效应,数字模块(从外部引脚移入数据或处理指令)和模仿模块(输出更新为新码)内部发生的一些能量会传输到外部。详细来说,首要有如下两种能量:数字馈通和数模转化毛刺能量。

在输出粗调状况下,其间一些能量被缓冲器的压摆率躲藏,因为这是将能量注入输出负载的首要奉献要素,而在微调更新状况下,这两种能量均可出现且能够丈量出来。

DAC内核动态效应

任何DAC操作都会发生内部电流或电压尖峰,这些尖峰必定经过电源引脚(一般是VDD或GND)耗散。因为内部寄生效应,DAC操作时内部发生的能量无法经过这些途径彻底耗散,部分能量会传输到输出负载,影响输出稳定性。

数字馈通是这样一种现象:在数据转化期间,外部数字引脚上的改变会搅扰内部DAC。

别的,外部印刷电路板(PCB)的不妥布局也或许会扩大数字馈通。

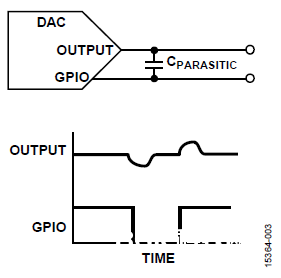

PCB布局的最佳做法是让PCB中的数字走线远离PCB模仿走线,或至少防止模仿走线与数字走线并行,以使外部耦合效应最小。图3显现了布局不妥引起数字馈通的一个比如。

图3.PCB上的容性效应

数字馈通是一个典型标准,因为传输到负载的能量取决于多个要素,例如数字输入电平、压摆率、信号发生改变的的数字走线数目(传输的数据)。

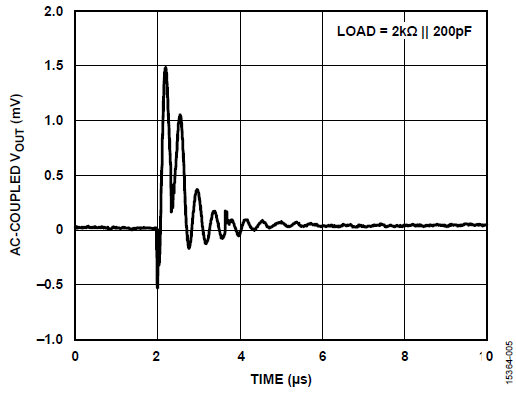

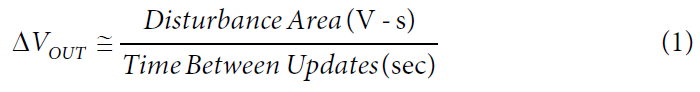

该标准丈量的是面积(nV-s)表征的是外部传输的能量。图4显现了一个与写入输入寄存器相关的数字馈通效应示例。

图4.数字馈通丈量示例——AD5686R

要丈量与数字馈通相关的能量,须向DAC写入一个指令但并不更新DAC内核输出(例如更新操控寄存器),避免丈量其他或许进步内部发生能量(即DAC内核更新时发生的能量)的效应,或丈量与任何内部校准例行程序相关的额定能量。

履行内部校准例行程序所发生的能量包含在数模转化毛刺中。数字馈通体现在每次读/写拜访中。

当DAC内核输出更新时,能够在DAC输出上观测到另一种动态现象以毛刺方式体现出来。此标准与DAC内核中内部开关操控线路之间的不同传达推迟有关,称为数模转化毛刺脉冲或毛刺能量,因为它是在数字字被转化为模仿信号(经过切换开关来挑选DAC电阻)时发生的。

数模转化毛刺脉冲是器材固有的,但假如PCB布局不妥,它会像数字馈通相同恶化。

数模转化毛刺脉冲的典型功能也用主进位跃迁1 LSB的净面积(nV-s)来衡量。关于一个16位DAC,主进位发生在DAC码0x7FFF和0x8000彼此切换之间,这一般会形成内部绝大大都DAC开关发生切换。

图5显现了一个与写入DAC寄存器相关的数模转化毛刺脉冲效应示例。若要无视数字馈通奉献,能够让DAC运用推迟硬件LDAC事情进行更新,即在数字馈通发生的能量彻底耗散之后进行更新。

图5.数模转化毛刺脉冲丈量示例——AD5686R

不同DAC码会发生不同的毛刺能量,因为码改变触及到不同的开关。

数模转化毛刺的最差景象并不一定是主码跃迁(中心位电平码的1 LSB改变)。这取决于两个要素:布局中的内部寄生效应和DAC(包含内部校准引擎)中的内部寄生效应。实践上,数字中心位电平码并不一定是中心位电平DAC码。但是,数字主码跃迁被认为是量化数模转化毛刺能量的一个很好的基准。

DAC内核动态效应的传达

输出端的压摆率和响铃振动是低频时的事情,而数字馈通和数模转化毛刺脉冲首要是中频到高频效应。

发生数字馈通的频率与数字传输有关,例如50 MHz时钟速度或更高速度。例如,压摆率为1 nV/s时,信号音能够高达300 MHz。图4和图5显现了动态事情频率所引起的可观测快速瞬变。

在所有状况下,内部发生的部分能量都能够在外部丈量,如上面的图形所示。传输到负载的动态能量取决于与输出引脚相连的外部电容,它会发生如下的电压增量:

从基准丈量成果能够看出,电压增量与外部衔接的电容是相对独立的,因为传输到外部的动态能量经过DAC输出引脚这一低阻抗途径进行耗散。

接连DAC操作

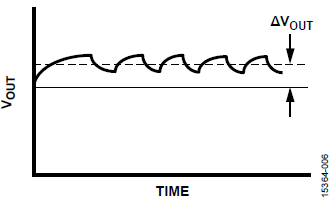

假如DAC在要求快速微调的运用中接连更新,则传输到负载的能量不会彻底耗散,故而在输出端会丈量到额定的偏移。

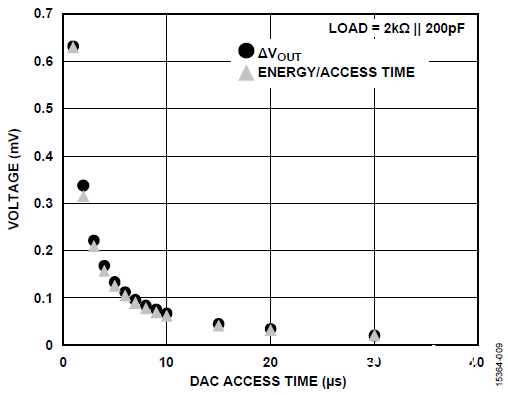

电压增量的值取决于两个要素:传输的能量值和电容的放电时刻,如图6所示。

图6.VOUT增量与更新速率的联系

假定DAC接连更新,则内部发生的能量是数字馈通和模仿毛刺一起效果的成果。

某些状况下,当DAC仅拜访读/写寄存器且不履行DAC内核更新操作时,电压增量仅由数字馈通引起。

AD5686R 4通道16位nanoDAC+事例研讨

为了阐明这些概念,下面以AD5686R为例进行阐明。

接连更新AD5686R输出会推迟写操作的间隔时刻,从1 μs到20 μs不等。

内部发生的能量在大约1 μs内传输出去,该时刻是数字馈通持续时刻、24位传输时刻(36 MHz SCLK时钟)和模仿毛刺持续时刻的总和。

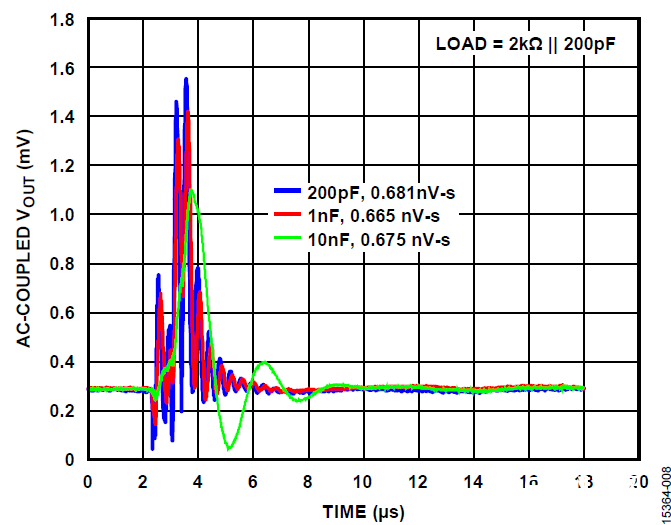

当更新时刻与能量事情类似,或比能量事情更长时,依据电容值(如图7所示),发生的电压增量可近似计算如下:

搅扰面积(V–s)

更新间隔时刻(s)

图7.不同负载电容下AD5686R的动态能量示例

1 μs更新一次时,测得的电压增量与数字馈通能量和模仿毛刺共同,0.13 nV-s + 0.5 nV-s = 0.63 nV-s,如图8所示。

图8.发生的ΔVOUT与DAC拜访时刻的联系

举个比如,若搅扰为0.63 nV-s,更新频率为2 μs,则发生的电压增量为:

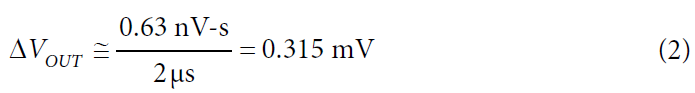

图9显现了基准丈量成果与等式1之间的共同性。

图9.实测ΔVOUT成果与运用等式1得到的估量值的比较——AD5686R

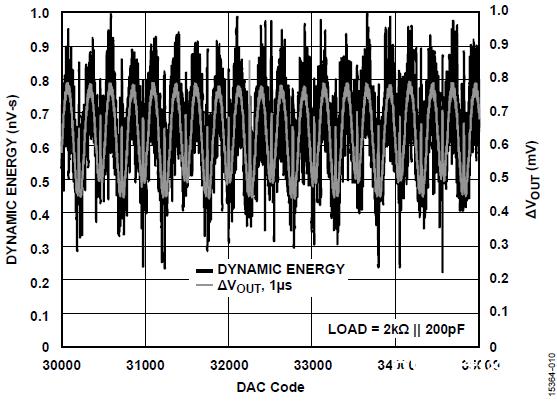

并非所有码都发生相同的净面积,ΔVOUT会略有差异。图10显现了中心电平邻近代码的成果示例。发生较高动态能量的代码也会体现出较高的ΔVOUT。均匀能量与AD5686R数据手册标准适当(约0.6 nV-s)。

图10.动态能量和ΔVOUT与DAC码的联系示例——AD5686R

要以高分辨率丈量动态能量,输出信号有必要沟通耦合。这样,当企图以快速拜访时刻丈量动态能量时,部分直流重量或许会丢掉。因而,当DAC拜访时刻过快导致此剩余能量无满足时刻耗散时,ΔVOUT(直流值)是量化此能量的更好办法。

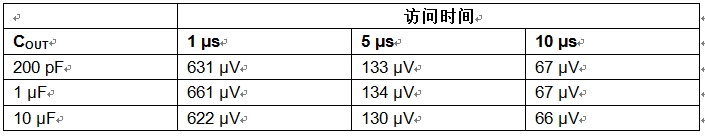

如前所述,测得的净面积与外部衔接的电容无关,如图7所示。

表1显现,给定拜访时刻时,在不同负载电容下测得的ΔVOUT略有差异。

表1.不同DAC拜访时刻和负载%&&&&&%对应的ΔVOUT值示例——AD5686R1

1输出负载 = 2 kΩ,SCLK = 36 MHz。每个器材丈量一个通道。

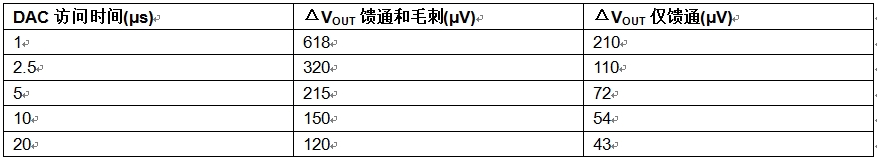

表2显现了AD5686R在不同DAC拜访时刻下测得的ΔVOUT:既有不同拜访时刻下数字馈通和数模转化毛刺脉冲两个要素引起的典型ΔVOUT成果(这种状况下更新DAC输出),也有仅数字馈通引起的成果(这种状况下DAC码写入输入寄存器,但输出不更新)。

表2.AD5686R1典型值

1输出负载 = 2 kΩ || 200 pF,SCLK = 36 MHz。

结语

因为动态现象的实质及其效应与寄生参量和耦合电路严密相关,它们在不同DAC上会有不同的体现。动态效应的改变取决于详细运用、电路装备和作业条件。

关于DAC输出的粗调更新,树立时刻和时延是DAC更新速率的约束要素。当仅触及DAC输出的微调时,或写入器材而不更新输出时,DAC内核动态效应发生的额定能量或许会引起一些额定偏移。

假如直流功能在运用中非常重要,请勿以最快速度(由数字接口决议)操作DAC。当运用清晰要求较快更新速率时,有必要评价能量面积以了解其对体系功能的潜在影响。要恰当地量化此影响,最佳做法是实践丈量。当体系中存在剩余直流电压(ΔVOUT)时,主张在不同拜访时刻下丈量该值,以便消除杂乱且相对不牢靠的沟通丈量需求。

一般来说,当运用DAC时,应细心评价动态功能(树立时刻、数字馈通和数模转化毛刺)及体系装备,以建立一个牢靠的拜访时刻(更新速率)。