电压毛刺脉冲在信号链途径中很常见,特别在体系加电或断电时更是如此。依据峰值起伏和毛刺脉冲持续时间的不同,体系输出中的终究成果会是灾难性的。其间的一个示例便是工业电机操控体系,在这个体系中,数模转换器 (DAC) 驱动电机驱动器,以操控电机旋转。假如毛刺脉冲起伏高于电机驱动器的灵敏度阈值,当体系加电/断电时,电机会在没有任何方向操控的状况下旋转。

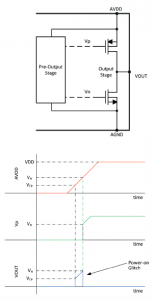

图1.经简化的输出级和加电毛刺脉冲

之前现已剖析了高精度DAC经缓冲输出呈现加电/断电毛刺脉冲的原因和削减这些毛刺脉冲的处理方案。这份简报首要介绍了DAC输出缓冲器在加电至电压输出形式时呈现的加电毛刺脉冲。一个高精度DAC能够在多个装备中加电:零量程、中量程,或是高阻抗。用户能够操控预断电状况。某些DAC具有内置的加电毛刺脉冲削减 (POGR) 电路;这个电路在DAC输出级未被驱动的装备中坚持DAC的输出级。经缓冲电压输出DAC具有一对作为输出级的PFET和NFET。POGR电路禁用PFET,并将NFET偏置到其阈值电压 (VTH) 以上,然后最大极限地将加电毛刺脉冲削减到几百毫伏。

并不是每个DAC中都有POGR电路。关于没有POGR的DAC来说,加电/断电毛刺脉冲取决于多个要素:

1.DAC到电压输出形式和高阻抗形式的加电状况

2.DVDD、VREF、IOVDD和其它电源引脚的加电次序

3.反应网络连接

4.电源斜升速率

5.输出阻性负载

这篇文章所评论的是输出级被加电至电压输出形式的状况。在这个形式下,PFET和NFET的栅极由一个预输出级操控。这个预输出级需求一个特定的最小电压来正常发动。这个电压也被称为最小净空 (VH)。这个电压取决于预输出级架构,而且可高至6V。这个电压远远低于数据表中所规则的最小电源电压 (VDDMIN)。一般状况下,大多数数据表中并未指定此电压。

在到达这个最小净空电压前,预输出级没有满足的净空来完成正常运转。因而,输出FET栅极能够低至0V,这使得PFET能够在电源电压与PFET阈值电压 (VTP) 相交时,运转为电源与输出引脚之间的低阻性开关。因而,输出能够跟着电源斜升,然后导致了加电毛刺脉冲(请见图1)。

在这个状况下,毛刺脉冲电压能够高达最小净空电压 (VH)。因为预输出级的净空缺乏,所以这个毛刺脉冲与电源斜升速率无关。一切DAC数据表都规则了一个输出上的最小阻性负载(一般为1kW)。将一个阻性负载加载到DAC输出上是尽可能减小这个毛刺脉冲的常见技能。但是,这项技能并不能最大极限地削减毛刺脉冲起伏,这是因为输出PFET运转为一个电源与输出引脚之间的开关(或短接)。加电序列和反应网络连接会进一步加大这个毛刺脉冲。因为这些要素一般是彼此相关的,它们都作为一种状况进行剖析。

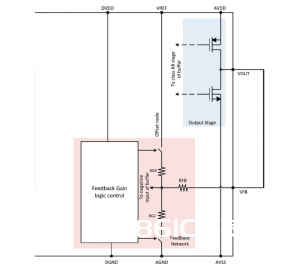

图2.具有反应网络的输出级。

关于具有双极输出的双电源DAC来说,反应网络还包含一个偏移节点。这个节点可由基准引脚上的固定电压 (VREF) 驱动,或许由一个偏移DAC驱动。偏移DAC在用户需求小电压偏移输出时有用,然后完成一个不对称的输出规模;例如,从-5V至+10V。

图2是一个具有反应网络的输出级的简化图。这个反应网络需求开关来改动DAC的增益和偏移。这些开关有一个独自的数字电源,或DVDD供电。依据DVDD加电序列的不同,增益/偏移途径会为开路,或许短接至VREF/AGND引脚。这会在发动期间导致一个过错增益设置,而且会构成加电毛刺脉冲。在大多数多电源DAC中,主张运用一个特定的加电序列来防止这一状况的产生。

加电毛刺脉冲与DAC寄存器的状况无关。在DAC有一个被称为加电复位 (POR) 的电路供电时,一切DAC寄存器均坚持在复位状况。当一段时间后,这些寄存器从复位状况中被开释出来时,输出和预输出级就具有满足的净空来正常运转了。

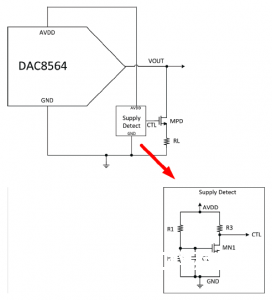

图3.简略电源检测电路

一个简略电源检测电路(图3)可被用来在电源斜升期间当即载入DAC输出。DAC输出VOUT在电源斜升期间,经过FET MPD,用电阻器RL载入。这个电源检测块生成MPD操控。在电源斜升期间,操控信号CTL被拉至AVDD,在FET MN1被接通前,用负载RL载入DAC输出VOUT。在MN1被彻底接通后,它将CTL节点拉至接地,卸载VOUT节点。有必要依据MN1的阈值电压来设定R1、R2、R3和CL的巨细。

这篇文章剖析了加电毛刺脉冲和它构成的根本原因。尽管其间的剖析首要是用来处理加电毛刺脉冲,不过相同的原理也适用于断电毛刺脉冲。特定DAC在没有内部POGR电路的状况下,在正常形式下被加电,在发动期间,输出引脚与接地之间的一个小的阻性负载是尽可能削减这些DAC加电毛刺脉冲的仅有办法。