就许多中央处理器 (CPU) 而言,标准要求电源有必要能够供给大而快速的充电输出电流,特别是当处理器改换作业形式的时分。例如,在 1V 的体系中,100 A/uS 负载瞬态或许会要求将电源电压稳定在 3% 以内。处理这一问题的要害便是要认识到 这不仅仅是电源的问题,电源分配体系也是一个重要因素,并且在一款处理方案中咱们是很难将这二者严格地划清界限。

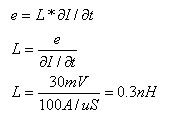

这些高 di/dt 要求的含义就在于电压源有必要具有十分低的电感。重新整理下面的公式并求解得到答应的电源电感:

在快速负载电流瞬态通道中电感仅为 0.3 nH。为了便于比较,咱们来看一个四层电路板上的0.1 英寸 (0.25 cm) 宽电路板线迹所具有的电感大约为 0.7 nH/英寸 (0.3 nH/cm)。%&&&&&% 封装中接合线的典型电感在1 nH 范围内,印刷电路板的过孔电感在0.2 nH 范围内。

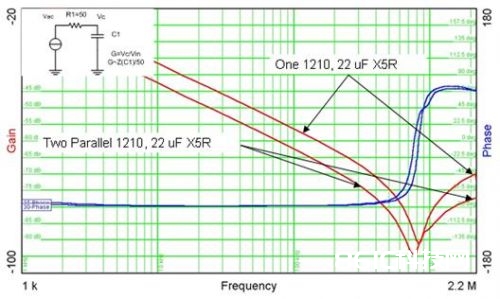

此外,还有一个与旁路电容有关的串联电感,如图 1 所示。顶部的曲线是贴装在四层电路板上的一个22 uF、X5R、16V、1210 陶瓷电容的阻抗。正如咱们所希望的那样(100 kHz 以下),阻抗跟着频率的添加而下降。但是,在800 kHz时有一个串联电感,此刻电容会变得有电理性。该电感(其能够从电容值和谐振频率核算得出)为 1.7 nH,其大大高于咱们 0.3 nH 的目标值。走运的是,您能够运用并联电容以下降有用的 ESL。图 1 底部的曲线为两个并联电容的阻抗。风趣的是谐振变得略微低了一些,这表明有用电感并不是肯定的一半。根据谐振频率,就两个并联的电容而言,新电感则为 1.0 nH 或ESL 下降 40%,而非下降 50%。这一成果能够归结为两个原因:互连电感和两个电容之间的互感。

图 1 并联电容阻抗寄生现象衰减作用

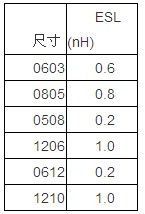

电流通道的环路尺度在必定程度上决议了衔接组件中的寄生电感,组件尺度决议了环路的面积。尺度与电感相关系数如表 1 所示,其显现了各种尺度陶瓷外表贴装电容的电容电感。一般来说,体积越大的电容具有更大的电感。该表不包括电路板上贴装电容的电感,在咱们曾经的丈量中该电感由 1 nH 添加到了 1.7 nH。另一个风趣的问题是端接的方位对电感有很大的影响。0805 电容在电容的较短一侧有端接而0508 电容则在较长的一侧有端接。这简直将电流通道分为了两半,然后大下降了电感。这种变化了的结构将电感下降了四分之一。

表 1 陶瓷 SMT 电容尺度会影响寄生电感

总归,高 di/dt 负载需求细心考虑旁路问题以坚持电源动态稳压。外表贴装电容需求十分接近负载以最小化其互连电感。电容具有或许防止很多去耦的寄生电感。下降这一寄生电感的并联电容是有用的,但互连和互感削弱了这一作用。运用具有更短电流通道的%&&&&&%也是有用的。这能够用体积较小的部件或具有沟通端接(其运用了更短的尺度用于电流)的部件来施行。