摘要:为减小基准电压源的差错,进步集成电路精度,规划了一种依据JTAG接口的熔丝烧断修调电路,侧重剖析JTAG接口及修调技能的详细完结。经过调整电路内部结构,使基准电压在-40到85度的范围内差错不超越100ppm,并经过流片验证了该规划的可行性。

集成电路的工艺差错问题是规划高精度电路的首要妨碍之一,为进步芯片的合格率,引进修调技能已成为完结高精度集成电路的必要手法。现在,常用修调技能包含电阻薄膜激光修调、熔丝烧断修调、二极管短路修谐和内嵌非挥发性存储单元的修调技能等。熔丝烧断修调一般选用大电流将熔丝电阻烧断,当修调开关少时,可引进额定的修调PAD并直接在PAD处烧写,再运用译码器。但当修调开关多时,附加的PAD会占用较大的芯片面积,为削减附加引脚或修调PAD,可运用移位寄存器经过串行接口输入数据并在芯片内部规划修调电路。为找到一组适宜的开关码并将其固定,电路需有移位查找、烧写及烧写后读值等作业形式。多重形式挑选必然添加外部操控引脚,为减小芯片面积,决议选用JTAG接口来完结对串行输入式熔丝烧断修调电路的操控,经过TAP操控器及指令寄存器来操控修调形式挑选。本文给出了一种依据JTAG接口的内建修调电路的规划办法,此次规划选用华虹0.35umBCD工艺完结并进行了流片验证,成果表明该电路彻底完结了规划功用。

1 JTAG接口电路的规划

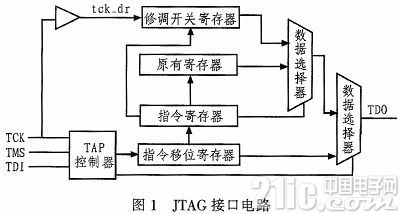

JTAG(Joint Test Action Group)联合测验举动小组)是一种国际规范测验协议(IEEE 1149.1兼容),首要用于芯片内部测验。规范的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为形式挑选、时钟、数据输入和数据输出线。本规划所需的JTAG接口由以下几部分组成:TAP操控器、指令寄存器及数据寄存器(这儿指修调开关寄存器),能够从图1中更直观的看出。

1.1 TAP操控器的规划

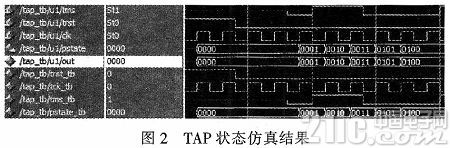

TAP操控器是一个同步状况机,把接收到的TMS和TCK信号译码,发生所需求的操作操控序列,操控电路进入相应的测验方法。设输入为tms,输出为state(即当时状况),界说next_state为下一状况。

编写程序及测验代码,包含一切TAP操控器的状况,从图2的仿真成果中能够看出,跟着时钟改变,state的状况在改变,TAP操控器的状况依照如下次序改变:TEST_RESET,TEST_IDLE,SELECT_IR,CAPTURE_IR,SHIFT_IR,EXIT1_IR,UPDATA_IR,SELECT_DR,CAPTURE_DR,SHIFT_DR,EXIT1_DR,UPDATA_DR,SELECT_DR,SELECT_IR,TEST_IDLE,回到TEST_RESET状况,与测验代码共同。

1.2 指令寄存器

指令寄存器是JTAG模型结构的重要组成部分,其操作有必要契合相关要求。本次经过取用指令寄存器的非公共指令部分界说新的指令用以操控修调电路的形式挑选,规划中指令寄存器实际上是两个等长的寄存器,即移位寄存器和输出寄存器。在SHIFT_IR状况下,数据由TDI移入移位寄存器,在更新IR状况下,数据由移位寄存器加载到输出寄存器。意图是防止在移位过程中呈现过渡数据影响体系功用。

1.3 数据寄存器

在本规划中需求用到一个修调开关寄存器,使用Spice软件进行规划,详细规划见第3节。但在验证JTAG接口功用时,需求模仿一个修调开关寄存器,给予这个假定的寄存器

相应的输入信号。依据IEEE1149.4鸿沟扫描规范,测验逻辑结构中至少要有一个旁路寄存器(Bypass Register)。一般当芯片不在测验形式的状况时则将JTAG装备为旁路形式。将这些数据寄存器置于共用的串行输入(TDI)和串行输出(TDO)之间,由指令寄存器操控扫描途径。

2 修调电路的规划

本次规划的中心是16位熔丝烧断修调操控电路,修调的对象是电压值为2.5000V的带隙基准,可应用于带隙基准电压源芯片或包含带隙基准的体系级芯片内部。经过修调使得在-40到85度的温度范围内,在各工艺角下电压与温度联系的仿真成果为呈现出近似抛物线的形状。

修调电路的全体结构如图3所示;端口包含TCK_DR、RST_N、TDI、SHIFT/LOAD、VCC_TRIM以及PRG_EN。其间TCK_DR选用独立时钟以防止和TCK保持共一起,修调开关寄存器在不需求的情况下作业时移位和烧写引起的差错。端口SHIFT/LOAD是数据挑选器的挑选端,操控信号由LOAD指令译码发生,只要在TAP为CAPTURE_DR状况且指令为READ_FUSE时为0,当指令为READ_FUSE且TAP状况为SHIFT_DR时移位,此刻TCK_DR是有用的。VCC_TRIM为烧写电源,PRG_EN为烧写使能。电路首要进入的是移位查找形式,将数据送入修调寄存器内,查找16个数字开关对应的值,只要在指令为LOAD_DS,且TAP状况为SHIFT_DR时移位。之后进入烧写形式,在烧写操控端有用时(PRG_EN只要在指令为TRIM且TAP状况为UPDATE_ IR时才为1),逐位依序进行烧写(烧断熔丝)。最终让其进入烧写成果读出形式,从TRIM_SD0端读出烧写的成果,假如正确,电路则进入正常作业状况。

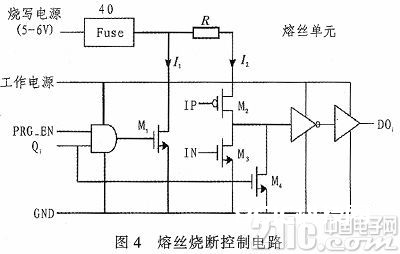

如图4为熔丝烧断操控电路。

本次选用的HHNEC工艺中的熔丝器材叫Fuse,是多晶资料做成的,初始电阻为40 Ω。当Fuse连入电路中时,经过核算熔丝烧断过程中流过Fuse上的电流应为125 mA,而且烧写使能需求继续5 ms的高电平才干烧断。当烧写操控端PRG_EN有用,且Qi为1时,M1管导通,此刻电路中要流过相当大的电流。熔丝烧断位所对应的二进制值为1,未烧断则为0。

3 仿真验证

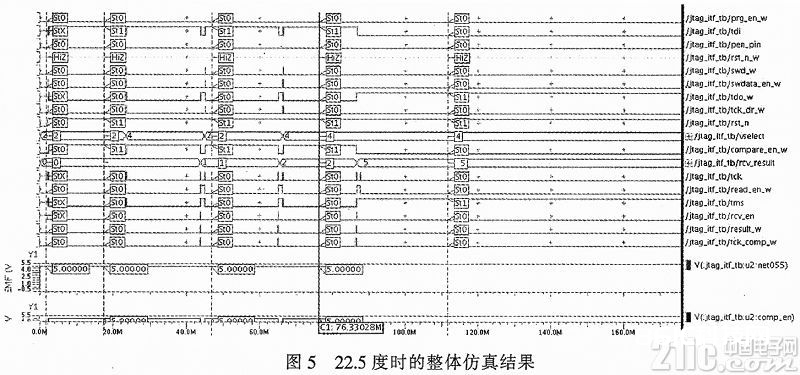

全体功用的验证是经过在虚拟机环境下运转AdvanceMS软件进行混合仿真完结的。混仿的数字部分首要是JTAG模块,模仿部分则经过Spice文件生成网表。在温度为22.5度时,经过测验找到了一组满意基准电压要求的开关组合为0X7FC0。在-40和85度温度下经验证仿真成果与22.5度时的相同。

4 定论

本文依据华虹0.35 μm BCD工艺成功完结了一种依据JTAG接口的内建熔丝烧断修调电路的规划。完结了外部操控器对电压源内部电阻串结构的操控,经过改变电开关组合然后调整电压值。使用ADMS软件进行混合仿真调试,最终得到一组满意要求的开关组合0X7FC0,在-40、22.5和85度下,差错不超越0.000 2 V。此规划已应用在一种回路供电外表专用芯片中,且芯片已流片成功,因而规划具有实际意义。

选用JTAG接口规划有用地减小了芯片面积,与激光修调比较,降低了设备费用本钱,而且完结多个芯片一起测验及放入温箱中一起进行修调,降低了芯片的修调时刻,进步了作业效率。