0 导言

频率是人们工作和日子傍边常用到的物理量之一。其间时刻、速度等物理量都能够用频率来表明。近年来跟着现代工业的开展,高精度的频率计得到广泛的注重与运用,比方各大高校和科研院所的实验室需求用到的频率计基准。可是现在能够满意高精度丈量要求的频率计结构杂乱而且价格昂贵,因而规划一款精度高、本钱低的频率计就非常必要了。

直接计数法是曩昔常常用到的丈量频率的办法。直接计数法包含两种丈量原理,一种丈量原理是在闸口时刻T不变的状况下,对被测频率进行计数,通过所计的脉冲数N与T的比值求出相应的频率值;另一种原理是在给定的一个被测信号周期内对规范频率进行计数,通过所计的数值N0与规范频率值求出被测频率。但它们都存在±1个字的计数差错。丈量精度低。其次是多周期同步丈量法,此办法又叫作倒数计数器法。它是现在频率丈量中运用最为广泛的测频办法。多周期同步丈量法的丈量原理是在若干个给定的被测信号的周期中对规范频率和被测频率一起计数,依据所测得数值求出被测频率。它让不同的被测频率与实践闸口同步,这样就去除了被测频率的±1个字的计数差错,但规范频率仍然还存在±1个字的计数差错。此外还有游标法和模仿内插法,这两种办法别离通过游标振荡器和内插器来减小±1个字的计数差错,能够到达很高的精度,可是仪器结构杂乱而且本钱很高。

本文运用相位检测技能,通过捕捉规范信号和被测频率的相位重合点,使这两个频率和实践闸口彻底同步,然后消除了规范频率和被测频率中的±1个字的计数差错,使丈量中的精确度能够到达10-10量级。但传统频率计的中心硬件规划大都运用16位单片机外接级联的计数器,这样不只使电路杂乱,引进不必要的差错,无法确保丈量精度,而且处理丈量数据速度过慢,在当今科研工作中现已无法到达科研人员的科研要求。本文在此基础上通过选用32位处理器ARM7作为主控芯片,比传统的16位单片机提高了控制系统和丈量数据处理的速度。

1 相频检测法原理及差错剖析

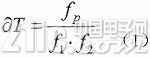

在相位检测法频率丈量中有一个重要的概念便是最大公因子频率。它的倒数为最小公倍数周期Tp。最大公因子频率的界说为:假如关于恣意两个频率信号和f1和f2,当f1=M f0,f2=Nf0;其间M和N这两个正整数没有公共的约数,那么f0便是f1和f2之间的最大公因子频率fp。两个信号的量化相移分辨率设为![]() ,其公式如下:

,其公式如下:

在一个Tp周期中有M个f1的周期或许N个f2的周期T2。假定M>N且以f2的上升沿作为参阅,那么量化后的f1和f2在一个Tp周期中有且只要N种相位差状况,而且每种状况在一个Tp周期中各不相同。若按巨细表明则为

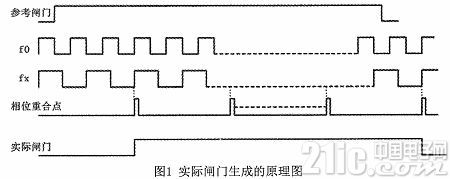

。当两个信号相位差非常小时,称之为相位重合点。相位检测测频的原理便是捕捉若干个相位重合点,在这些相位重合点之间有完好的整数倍规范信号和被测信号的周期,以此来设定实践的闸口时刻。这样就能够消除规范频率和被测频率中都存在±1个字的计数差错。图1为实践闸口生成的原理图。

从图1能够看出,当参阅闸口翻开之后,首个相位重合点到来时,实践闸口开端计数,当参阅闸口闭合后首个相位重合点到来时,实践闸口闭合中止计数。当实践闸口敞开时,计数器开端别离对规范频率和被测频率计数,假定规范信号脉冲个数为N0,被测信号脉冲个数为Nx,那么被测信号频率值为:

因为δQ要远远小于Tx和T0,所以此办法能够取得适当高的丈量精确度。在多周期同步丈量中的相对差错与式(6)相同。其间的δN0=±1而δNx=0,所以此倒数计数器法在省掉规范频率的影响下丈量相对差错为:

由式(11)可知,被测信号的相对差错由规范信号的周期的±1倍所引起。因而将被测频率与规范频率一起同步后丈量的值要更精准。

2 硬件电路规划

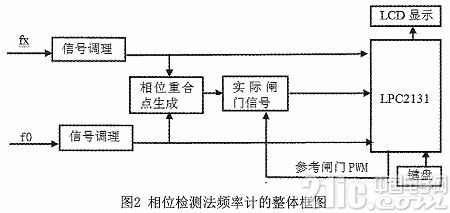

图2为相检频率计的全体框图。因为被测信号要求最大丈量频率为10MHz,丈量精度到达10-10量级,因而规范信号频率精度要至少到达10-11量级。根据此本文选用安捷伦公司出产的恒温晶振10811A作为规范频率的输出设备,其最大输出频率为10MHz,准确度优于10-11。一起其具有体积小、便于产品规划的长处,因而满意规划要求。

其间频率通过信号调度电路的意图是对输入的信号进行必要的整形与扩大。它的输入阻抗以及输入电压的灵敏度要高,以及能够调度各种波形的周期性信号,其间杰出的抗搅扰才能也是必不可少的。因而本规划挑选运用比较器ADCMP604完成信号调度功用,将信号整形为方波信号。ADCMP604的延迟时刻大约为1.6ns,与被测信号10MHz比较能够忽略不计。与此一起,电路在按捺共模搅扰方面决议选用LVDS差分信号输出来完成。电路图如图3所示。其间Vp端接被测信号,Vn端接地,当fx大于0时,Q端输出为高电平,当fx小于0时,Q端输出为低电平。