DTMF的介绍

1.1 DTMF承受的频率规范

DTMF(双音多频)信号是电话网中常用的信令。DTMF拨号和解码在通讯体系及其它方面有着广泛的运用。无论是家用电话、移动电话仍是程控交换机上,多选用DTMF信号发送接纳号码。DTMF技能还能够用于电力线载波通讯等场合。

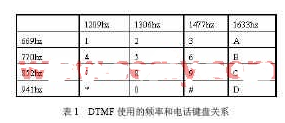

DTMF运用两个频率在电话体系中传输信息,表一中显现了运用频率和电话键盘的联系。

1.2 DTMF承受的时刻序列规范

依据ITU-T Q.24主张,DTMF信号的技能目标是:传送/接纳率为每秒10个号码,或每个号码100ms。每个号码传送进程中,信号存在时刻至少45ms,且不多于55ms,100ms的其他时刻是静音。在每个频率点上答应有不超越±1.5%的频率差错。任何超越给定频率 ±3.5%的信号,均被认为是无效的,回绝供认接纳。别的,在最坏的检测条件下,信噪比不得低于15dB。

2 DTMF全体规划思维和办法

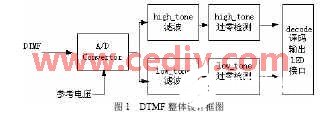

要规划一个能够完结DTMF信号的接纳及判别电路体系,能够考虑的计划有许多,能够挑选运用MCU编程完结,运用DSP编程完结,可是为了完结较好的功用,以及合理的电路结构,规划选用了纯数字电路的完结办法。规划的首要功用是完结经A/D采样的数字信号的滤波和频率判别,检测整个信号的时序并完结接口操控。全体规划如图一所示。其间:

1)high_tone滤波和low_tone滤波完结数字信号的滤波(运用FIR规划BPF模块完结)。

2)high_tone过零检测和low_tone过零检测依据过零率巨细来检测信号的频率。

3)decode成果输出部分完结译码并一起选用LED进行显现。

从上面的全体规划框图中能够看出,整个规划的中心部分在于完结输入DTMF信号的带通滤波,在完结信号的AD改变后,能够有用的滤除带外的噪声,一起输出反映DTMF信号的过零率的数字信号,便于后续的模块完结频率判别和时刻序列的判别。下面别离介绍一下BPF滤波器,过零检测和时刻序列判别的详细规划进程。

3 有限冲击呼应来完结BPF滤波器的规划

3.1 BPF规划原理

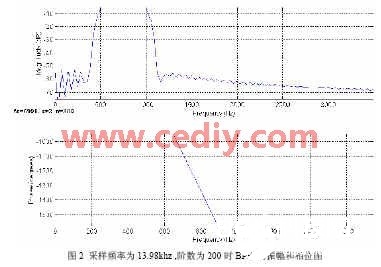

带通滤波器首要是用FIR(Finite Impulse Response有限冲击呼应)来完结了两个带通滤波器(HIGN_TONE_BPF ,LOW_TONE_BPF),首要功用为完结两组带通频率1100hz-1700hz,500-1000hz,别离来滤波DTMF信号的高频率组和低频率组信号。高组信号的频率为1209,1336,1447,16633hz,低组信号的频率为697,770,852,941hz。BPF的采样频率为13982.6hz(同AD改变的频率共同)。经过将输入采样频率为13.98Khz,10位A/D采样后的数字信号滤波,使有用的DTMF信号经过,将输入信号的噪声滤除,输出反映输入信号正负的过零信号,以供接下来的信号检测部分用于频率判别和时序判别。BPF处于整个规划的方位在图一中为high_tone滤波和 low_tone滤波。其规划要求的首要希望特性如表二和表三所示。

3.2 BPF规划完结

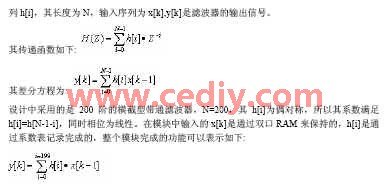

BPF模块是经过横截型FIR来完结带通滤波的。FIR滤波器的单位冲击呼应是一个有限长序

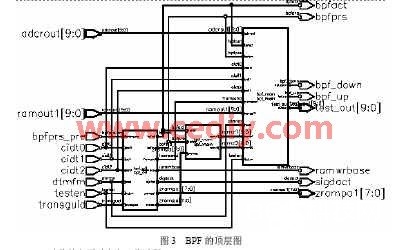

模块的振幅和相位特性如图二所示,规划中运用的FIR的系数是经过MATLABLE来规划完结的,首要是运用了MATLABLE中的FIR1这个TOOLBOX。BPF 顶层图如图三所示。

3.3 BPF动作的首要时序和作业进程

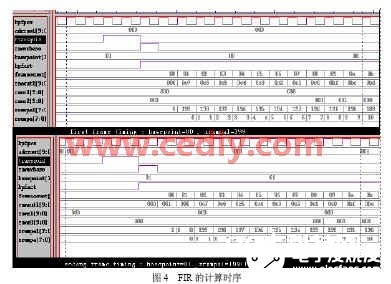

为了比较好的描绘BPF动作的首要时序,把图三中用到的一些首要信号界说介绍一下。

BPFPRS :整个规划数字电路作业的根本时钟

ADCROUT :A/D 采样成果输出,为10bit

TRANSGUID:A/D改变点

RAMWRBASE:RAM写信号,坚持一个时钟周期

BASEPOINT:FIR核算起始点,每一个新的A/D成果添加1

BPFACT:BPF核算容许信号,容许进行FIR核算

RAMOUT1:RAM输出,顺次输出前200个A/D成果

ROMZ1:FIRROM系数表1,为low_tone_bpf参数

ROMZ2:FIRROM系数表2,为high_tone_bpf参数

ZRAMPA1:RAM地址,每一个时钟递减1

ZROMPA:FIRROM系数表地址,每一个时钟递加1

作业进程描绘如下:BASEPOINT记录了进行FIR核算的现在时刻,即差分方程 的I,然后在RAMWRBASE下写入RAM,ZRAMPA1每一个时钟递减1,ZROMPA每一个时钟递加1,将H(I),X(N-I)输入,在BPF_MAIN模块中完结FIR的核算。FIR核算的详细进程描绘如下:1)读出RAM的A/D成果和BPF_VROM中的FIR系数 2)取出RAM和FIR系数的起伏和正负3)完结RAM和FIR系数起伏的乘法4)由RAM和FIR系数的正负,将乘法成果进行补码改变5)完结一切乘法成果的加法6)鄙人一个A/D到来完结时,将上一次的核算成果输出。典型的FIR的时刻序图如图四所示。图四中表明了BASEPOINT=0和1两种情况下FIR核算时序。

4 过零检测的规划和时刻序列的判别

经过带通滤波器后,实践输出为反映DTMF信号的数字信号,为此能够选用十分简略的,一起运用数字电路十分简略完结的非相干解调。非相干解调算法有过零检测法和包络检测法:过零检测法的根本原理是依据频键控信号过零率的巨细来检测已调信号中频率的改变。 输入已调信号经过限幅,滤波等构成与频率改变相应的必定宽度的矩形波,然后进行抽样判定,即可得到原始的调制信号。过零检测法用硬件电路来完结。这个检测电路模块的首要功用包含1)判别经过BPF滤波输出的高频率段和低频率段信号,判别输入的DTMF信号的频率是否在容许的差错规模内,假如输入的频率超越容许规模,不进行判别。2)一起经过规划不同的数字计数器完结时刻序列的查看,将满意时序要求的信号成果译码;假如不满意ITU-TQ.24的要求的序列,不输出成果。3)完结译码成果并一起选用LED进行显现。所以整个模块就是在输入信号的起伏满意电话传输要求,输入信号频率在容许的偏移内,在规则的输入信噪比下,能够正确的承受和判读输入信号,并译码进行显现。

5 总结

整个电路规划都选用的是纯数字方法,选用VHDL (Very high speed integrated circuit Hardware Description Language硬件描绘言语)编写了整个数字电路的完结,一起在MAXPLUSII平台下进行了仿真,证明了电路的功用达到了预期的意图。一起运用 FPGA (Field Programmable Gate Array现场可编程门阵列)完结了整个电路。在实践的测验中,达到了ITU-T Q.24所要求的“For the codes 0-9,*, # A-D, 1 false/1500 calls”的规划目标。

本文立异点在于整个规划选用了纯数字方法,完结简略。一起因为在规划中选用了硬件描绘言语编写了整个数字电路,所以整个电路便于移植,在运用时能够作为一个独自的模块,也能够作为其他规划中的一部分,十分灵敏。

责任编辑:gt