导言

数据收集体系是核算机测控体系中不可或缺的组成部分,是影响测控体系的精度等性能方针的要害因素之一。常用数据收集计划是以微处理器为中心操控多个通道的信号收集、预处理、存储和传输,即用软件完结数据的收集,这在必定程度上限制了数据收集的速度、功率及时序的精确操控。本文研讨的数据收集体系应用于某高速高精IC设备,待收集信号来源于多个传感器,体系要求在不多于180us的时刻内需完结悉数40路通道数据的现场高精度收集、预处理、实时存储及长途传输。考虑到FPGA器材的高集成度、高时钟频率、时序操控精确、编程灵敏等显着优于一般微处理器的特色,故本体系选用FPGA为中心操控ADC和数据传输,这样可到达预期要求,并简化外围电路,下降规划危险,缩短开发周期。

1体系结构

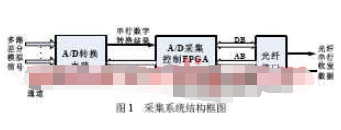

本文规划的数据收集体系划分为A/D转化电路、收集操控FPGA和光纤传输接口等若干部分,以A/D转化电路、收集操控FPGA为本收集体系的中心,如图1所示。

该体系完结数据的收集、预处理和存储功用。当收集操控FPGA经光纤接口接纳到来自长途伺服操控板卡的开端收集指令,来自各个传感器的差分模仿信号即经体系内的多路开关被选通地输入模数转化器,转化成果然后被引进收集操控FPGA中,在进行恰当的预处理后,数据被存储在FPGA内嵌的DPRAM中等待读取。一起依据对FPGA内建的存放器操作完结收集体系的其他功用,如复位、标定等。全体系12位有用数位的转化精度由高精度A/D芯片以及对模仿差分信号输入途径的标定来确保。

2要害芯片介绍

该数据收集体系涉及到的要害芯片首要为FPGA、ADC转化芯片。

FPGA选用Altera公司的EP1K100系列。该系列芯片选用查找表(LUT)和EAB(嵌入式阵列块)相结合的结构,内核选用2.5V电压,功耗低,可以供给高达250MHz的双向I/O功用,支撑3.3V/5V混合电压信号,无需额定电平转化芯片进行电平匹配。其特色正合适应用于具有杂乱逻辑及有存储、缓冲才能的数据收集体系。

Crystal公司的CS5101A是一款16位高精度CMOS模数串行转化芯片,内含双通道输入多路开关、ADC、转化和校准微操控器、时钟发生器、比较器和串行通讯口,其固有的采样结构使其作业时无需外部跟和顺坚持运放器。CS5101A的线性度差错为±0.001%FS,满刻度差错为±1LSB,转化频率为100KHz,具有自校准、抗温漂特性,长时刻空载可保持精度不变。选用该高性能ADC芯片对完结收集体系的精度校准和确诊效果有重要含义。

3计划完结

3.1 电路规划

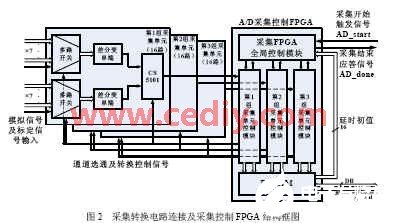

体系以8通道差分多路开关ADG407、差分运放器INA105和CS5101A构成收集操控FPGA的信号输入通道,如图2所示。该收集体系需求有40路差分模仿电压信号输入,故运用6片ADG407以完结最大48路模仿输入通道的多路复用。每片ADG407的输出连接到一个0.5倍差分运放器INA105完结差分至单端转化,通过运放网络后连接到CS5101A的一个模仿输入端。该收集体系运用3片CS5101A,别离对应3个收集子单元,至多可满意48路输入通道的要求。在一个采样周期内,挑选哪路差分模仿信号进行A/D转化由收集操控FPGA通过操控每片ADG407的地址挑选端和每片CS5101A的通道挑选端完结。电路及FPGA结构框图见图2所示。

精度是该数据收集体系的要害方针,规划的方针之一便是使整个收集体系能到达12位有用数位的转化精度。由CS5101A的参数得出该芯片的精度可达15位有用数位,故该体系的精度首要取决于信号的输入途径,即有必要考虑到板卡上的元器材作业情况和线路上信号传输对实践转化精度的影响,因而完结收集通道的标定关于整个收集体系有重要的含义。每一组模仿输入信号均要经多路开关,到一个前置扩大电路,再进入ADC中。该信号途径即为待标定的通道。当多路开关通道之间的匹配较好时,一路通道一次即可标定该组多路开关的一切通道。在此挑选每片ADG407的最终一路输入通道作为其标定通道,以收集体系板卡供给的零位电压(模仿地)和差分参阅电压为其输入信号,然后进行ADC全体精度的校准和确诊。

在上述规划下,将CS5101A的BP/UPN引脚拉高使其作业在双端状况。并通过设置其SCKMOD引脚和OUTMOD引脚电平使CS5101A作业在PDT(管道数据传输)的串行数据输出形式下,以利FPGA的时序操控。在此形式下,收集操控FPGA为CS5101A供给串行数据输出时钟信号SCLK,在转化时刻存放当时数据,然后鄙人一个转化周期输出上一次转化成果。CS5101A的/HOLD信号有必要在前次转化的数据出现在SDATA引脚之前坚持为低电平,以激起下一次转化。体系选用8.192MHz的石英晶振器为CS5101A供给时钟信号。

3.2 FPGA规划

收集操控FPGA的大局时钟频率为20MHz,其首要的I/O 引脚包含3组CS5101A的操控信号和ADG407的通道挑选信号,以及与光纤接口通讯用的32位数据总线、8位地址总线、读写操控线和收集开端/完毕信号。信号具体描绘如下。

SCLK : ADC串行转化成果在此输入信号的下降沿改动,在上升沿有用。

SDATA :在SCLK的下降沿输出数据位,可在SCLK的上升沿对数据进行有用锁存。

/HOLD :该引脚的下降沿将CS5101A设定为坚持状况并触发一个转化。

/STBY :在ADC复位后指示校准状况。在校准期间坚持低电平,校准完毕回来高电平。

/RST :低电平复位。回复高电平时触发一完好的校准序列波。校按时疏忽/HOLD信号。

CH1//2 : ADC内部的2个模仿输入通道的操控线。

ADCx_SEL[2:0] :用于模仿多路复用器(多路开关)输入通道挑选的操控线。

如图2所示,此FPGA顶层可分为3部分:大局操控模块F_ADC_ctrl、对应3个收集子单元的操控模块Sub_ADCx_ctrl(x=1~3,下同)和DPRAM模块。其间F_ADC_ctrl模块检测来自光纤接口的收集触发信号(F_ADC_start),并依此发生Sub_ADCx_ctrl子模块的开端作业信号(Sub_ADCx_start),在接纳到这三个子模块回来的转化完毕信号(Sub_ADCx_done)后,向光纤接口宣布收集完毕信号(F_ADC_done)以告诉长途伺服操控板卡读取收集成果,完结一次伺服周期的数据收集。在DPRAM模块内完结一切存放器。

别离操控3个收集子单元的Sub_ADCx_ctrl子模块是该FPGA的中心,每个模块可进一步细分为Sub_ADCx_Channel_sel模块和Sub_ADCx_Sample模块,这二者之间由Sub_ADCx_start_S2P信号和谐时序联系。该模块的结构框图如图3所示。

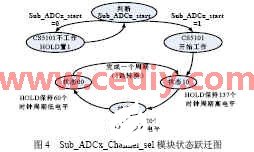

其间,Sub_ADCx_Channel_sel模操控CS5101A的/HOLD信号时序(Sub_ADCx_HOLD)和双通道挑选信号(Sub_ADCx_CH1_2)。作业状况如图4所示,其间/HOLD信号的高/低电平所保持的时钟周期数依据FPGA的大局时钟频率核算而定。Sub_ADCx_Sample模块则在Sub_ADCx_start_S2P信号的操控下输出大局时钟4分频的SCLK信号给CS5101A,并在SCLK的第66个上升沿完结收集成果的串并转化,一起输出与当时收集通道对应的地址给DPRAM模块,在SCLK的第70个上升沿发生对DPRAM模块的写使能信号Sub_ADCx_wr,然后将16位收集成果写入DPRAM模块内的指定空间。完结写操作后由Sub_ADCx_Channel_sel模块向F_ADC_ctrl模块提交转化完毕信号Sub_ADCx_done。

DPRAM模块内部存储地址与收集/标定通道一一对应,完结对转化成果的预处理(如阀值比较等)和锁存。另一端通过32位双向数据总线和8位地址总线与光纤接口通讯,以完结长途伺服操控板卡读取模块内的转化数据和读、写存放器。其间,写收集操控存放器改动其特定位的电平输出可完结对通道标定和数据收集操作的切换,以及体系复位等功用。鉴于该收集体系对数据实时性的要求,在DPRAM模块中还建有一个16位延时存放器(AD_delay_reg),其效果是供给F_ADC_ctrl模块内减1计数器的计数初值,以操控从检测到开端收集触发信号F_ADC_start到指令3个收集子模块真实开端收集之间的延时。关于有固定伺服周期T的伺服体系而言,完结一次全通道收集的时刻A和数据处理的时刻D相对安稳,则可由C=T-A-D得出预期延时时刻,如此可确保收集完毕和数据读取之间的时刻距离最小化,到达获取实时收集数据的要求。

4 FPGA模块操控时序

图5为针对Sub_ADC1_Channel_sel模块的仿真时序,成果显现了该模块可以精确发生CS5101A内双通道挑选信号CH1_2、/HOLD信号以及多路开关的操控信号。

图6为针对Sub_ADC1_Sample模块的仿真时序,波形包含了该模块的两个完好作业周期,成果显现该模块可以在和谐信号的触发下精确输出SCLK时钟和对DPRAM的写使能信号,以及待写入DPRAM的并行转化数据。

5完毕语

本文提出了一种以FPGA为中心操控CS5101A模数转化芯片完结多通道高精度数据收集体系的计划,并具体说明晰电路和FPGA的规划办法。通过长时刻测验,该收集体系各通道高速数据流可以正确收集和存储,作业安稳,且通道标定功用的完结使规划到达了希望的12位有用数位的精度要求,现已应用于某高速高精IC设备上。

责任编辑:gt