低功耗是MCU的一项非常重要的目标,比方某些可穿戴的设备,其带着的电量有限,假设整个电路耗费的电量特别大的话,就会经常呈现电量缺乏的状况,影响用户体会。

平常我们在做产品的时分,根本的功用完成很简单,但只需触及低功耗的问题就比较扎手了,比方某些可以低到微安级的MCU,而自己规划的低功耗怎样测都是毫安级的,电流居然可以高出规范几百到上千倍,遇到这种状况千万不要怕,只需仔细你就赢了。下边我们仔细分析一下这其间的原因。

第一条:掐断外设命脉——封闭外设时钟

先说最直观的,也是工程师都比较留意的方面,便是封闭MCU的外设时钟,关于现在市面上呈现的大多数的MCU,其外设模块都对应着一个时钟开关。只需求翻开这个外设的时钟,就可以正常的运用这个外设了,当然,此外设也就会发生相应的功耗;反之,假设想要让这个外设不发生功耗,只需封闭它的时钟即可。

第二条:让作业节奏慢下来——时钟不要倍频

除了外设模块功率耗费之外,还有一个功耗大户需求留意一下,这便是PLL和FLL模块。PLL和FLL主要是用来对原始的时钟信号进行倍频操作,然后进步体系的全体时钟,相应的,其功耗也会被提上去。所以在进入低功耗之前,需求切换是种形式,旁路掉PLL和FLL模块,然后尽可能的下降MCU的功耗,比及MCU唤醒之后再把时钟切换回去。

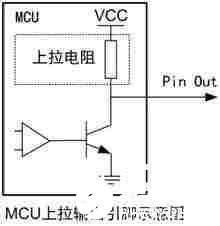

假设以为只需封闭外设时钟就可以确保外设不再耗电,那么你就太单纯了。假设IO口没有做好处理的话,它就会在暗地里偷走功耗,而你却浑然不知。详细原因是这样的,一般的IO的内部或许外部都会有上下拉电阻,举个比如,如下图所示,假设某个IO口有个10KΩ的上拉电阻,把引脚拉到3.3V,但是当MCU进入低功耗形式的时分,此IO口被设置成输出低电平,依据欧姆定律,此引脚就会耗费3.3V/10K=0.33mA的电流,假设有四、五个这样的IO口,那么几个mA就贴进去了,太惋惜了。所以在进入低功耗之前,请逐一查看IO口的状况:

假设此IO口带上拉,请设置为高电平输出或许高阻态输入;

假设此IO口带下拉,请设置为低电平输出或许高阻态输入;

总归一句话,不要把上好的电流糟蹋在发生热量的功用上,咱可不靠这点温度去暖手。

第四条:睦邻友好合作——留意I/O与外设IC的统筹

IO口的上下拉电阻耗费电流这一要素相对比较显着,下边咱来说一个不显着的要素:IO口与外部IC相连时的电流耗费。假设某个IO口自带上拉,而此与IO相连的IC引脚偏偏是自带下拉的,那么不管这个引脚处于什么样的电平输出,都不可避免的发生必定的电流耗费。所以但凡遇见这一类的状况,首要需求阅览外设IC的手册,确定好此引脚的的状况,做到心中有数;然后在操控MCU睡觉之前,设置好MCU的IO口的上下拉形式及输入输出状况,要确保一丝儿电流都不要被它耗费掉。

第五条:断开调试器衔接,不要被假象所利诱

还有一类比较独特,检测出来的电流耗费很大,可实践结果是自己杞人忧天,什么原因呢?是因为在测验功耗的时分MCU还衔接着调试器呢!这时分大部分电流就会被调试器给掳走,无缘无故的让工程师发生极度抑郁的心境。所以在测低功耗的时分,必定不要衔接调试器,更不能边调试边测电流。

总结

MCU的低功耗规划是一个详尽活,要养成杰出的习气,做到每增加一个功用都要从头验证一下低功耗是否符合要求,这样就可以随时随地干掉耗费功率的要素。假设把一切功用都规划好了才去考虑低功耗的问题,一个不小心,就可能要更改程序的架构——即便如此也不必定能把功耗给完全降下去。

责任编辑;zl