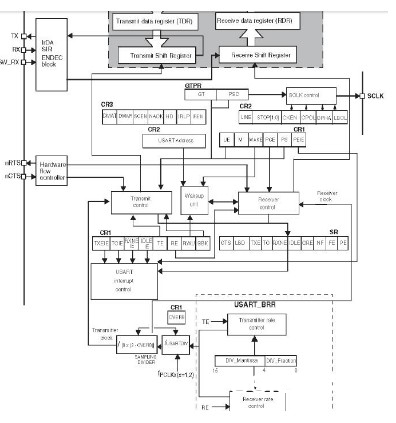

USART又名通用同步异步收发器,塔供给了一种灵敏的办法与工业运用标准NRZ异步春航数据格式的外部设备之间进行全双工数据交换。USART运用分数波特率发生器供给宽规模的波特率挑选,支撑同步单向通讯和半双工单线通讯,也支撑LIN(部分互联网),智能卡协议和IrDA(红外数据安排)SIR ENDEC标准以及调制解调器(CTS/RTS)操作,它还答应多处理器通讯,运用多换成器装备的DMA办法,能够完结高速数据通讯。

USART存放器操控框图如下

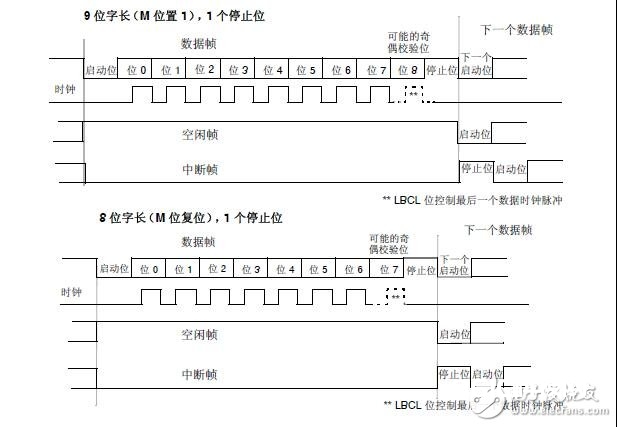

可经过对 USART_CR1 存放器中的 M 位进行编程来挑选 8(置0) 位或 9(置1) 位的字长。TX 引脚在开端位作业期间处于低电平状况。在间断位作业期间处于高电平状况。

闲暇字符可理解为整个帧周期内电平均为“1”(间断位的电平也是“1”),该字符后是下一个数据帧的开端位。

间断字符可理解为在一个帧周期内接纳到的电平均为“0”。发送器在间断帧的结尾刺进 1 或 2 个间断位(逻辑“1”位)以承认开端位。

发送和接纳由通用波特率发生器驱动,发送器和接纳器的使能位别离置 1 时将生成相应的发送时钟和接纳时钟。

字符发送

USART 发送期间,首要经过 TX 引脚移出数据的最低有用位。该形式下,USART_DR 存放 器的缓冲区 (TDR) 坐落内部总线和发送移位存放器之间。

每个字符前面都有一个开端位,其逻辑电平在一个位周期内为低电平。字符由可装备数量的间断位间断。

USART 支撑以下间断位:0.5(智能卡形式下接纳数据运用)、1(默许)、1.(智能卡形式下发送与接纳运用)5 和 2(正常USART形式,单线形式和调制解调器形式支撑该值) 个间断位。

留意:数据发送期间不该复位 TE 位。发送期间复位 TE 位会冻住波特率计数器,然后将损坏 TX 引 脚上的数据。当时传输的数据将会丢掉。

使能 TE 位后,将会发送闲暇帧。

间断位的装备

进程:

1.经过向%20USART_CR1%20存放器中的%20UE%20位写入%201%20使能%20USART。

2.%20对%20USART_CR1%20中的%20M%20位进行编程以界说字长。

3.%20对%20USART_CR2%20中的间断位数量进行编程。

4.%20假如将进行多缓冲区通讯,请挑选%20USART_CR3%20中的%20DMA%20使能%20(DMAT)。依照多缓冲区%20通讯中的解说阐明装备%20DMA%20存放器。

5.%20运用%20USART_BRR%20存放器挑选所需波特率。

6.%20将%20USART_CR1%20中的%20TE%20方位%201%20以便在初次发送时发送一个闲暇帧。

7.%20在%20USART_DR%20存放器中写入要发送的数据(该操作将清零%20TXE%20位)。为每个要在单缓%20冲区形式下发送的数据重复这一进程。

8.%20向%20USART_DR%20存放器写入最终一个数据后,等候至%20TC=1。这表明最终一个帧的传送已%20完结。制止%20USART%20或进入暂停形式时需求此进程,以防止损坏最终一次发送。

单字节通讯

一直经过向数据存放器写入数据来将%20TXE%20位清零。

TXE%20位由硬件置%201,它表明:

●%20数据已从%20TDR%20移到移位存放器中且数据发送已开端。

●%20TDR%20存放器为空。

●%20USART_DR%20存放器中可写入下一个数据,而不会掩盖前一个数据。

TXEIE%20方位%201%20时该标志位会生成间断。

发送时,要传入%20USART_DR%20存放器的写指令中存有%20TDR%20存放器中的数据,该数据将在当%20前发送完毕时复制到移位存放器中。

未发送时,要传入%20USART_DR%20存放器的写指令直接将数据置于移位存放器中,数据发送开%20始时,TXE%20位当即置%201。

假如帧已发送(间断位后)且%20TXE%20方位%201,TC%20位将变为高电平。假如%20USART_CR1%20存放器%20中的%20TCIE%20方位%201,将生成间断。

向%20USART_DR%20存放器中写入最终一个数据后,有必要等候至%20TC=1,之后才可制止%20USART%20或使微操控器进入低功率形式。

TC%20位经过以下软件序列清零:

1.从%20USART_SR%20存放器读取数据

2.%20向%20USART_DR%20存放器写入数据

留意:还可经过向%20TC%20位写入“0”将其清零。主张仅在多缓冲区通讯时运用此清零序列。

间断字符

将 SBK 方位 1 将发送一个间断字符。间断帧的长度取决于 M 位。(见上图USART字符阐明)

假如 SBK 方位“1”,当时字符发送完结后,将在 TX 线路上发送一个间断字符。间断字符 发送完结时(发送间断字符的间断位期间),该位由硬件复位。USART 在上一个间断帧的 结尾刺进一个逻辑“1”位,以保证辨认下个帧的开端位。

留意:假如软件在间断发送开端前对 SBK 位进行了复位,将不会发送间断字符。关于两个接连的中 断,应在上一个间断的间断位发送完结后将 SBK 方位 1。

闲暇字符

将 TE 方位 1 会驱动 USART 在第一个数据帧之前发送一个闲暇帧。(见上图USART字符阐明)

字符接纳(位数取决于M位)

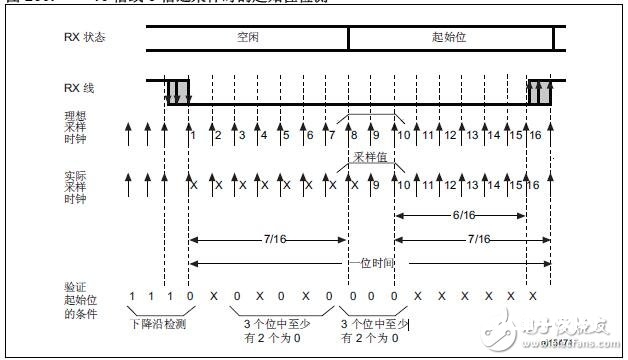

开端位检测

不管设置为16 倍或 8 倍过采样时,开端位检测序列相同都以16倍过采样检测。

在 USART 中,辨认出特定序列的采样时会检测开端位。该序列为:1 1 1 0 X 0 X 0 X 0 0 0 0。

留意:假如序列不完整,开端位检测将间断,接纳器将回来闲暇状况(无标志方位 1)等候下降沿。

假如 3 个采样位均为 0(针对第 3 位、第 5 位和第 7 位进行初次采样时检测到这 3 位均为 0; 针对第 8 位、第 9 位和第 10 位进行第2次采样时检测到这 3 位均为 0),可承认开端位 (RXNE 标志方位 1,RXNEIE=1 时生成间断)。

假如两次采样时(对第 3 位、第 5 位和第 7 位进行采样以及对第 8位、第 9 位和第 10 位进 行采样),3 个采样位中至少有 2 个为 0,则可验证开端位(RXNE 标志方位 1,RXNEIE=1 时生成间断)但 NE 噪声标志方位 1。假如不满足此条件,则发动检测间断,接纳器回来空 闲状况(无标志方位 1)。

假如其间一次采样时(对第 3 位、第 5 位和第 7 位进行采样或对第 8 位、第 9 位和第 10 位 进行采样),3 个采样位中有 2 个为 0,则可验证开端位但 NE 噪声标志方位 1。

字符接纳

USART 接纳期间,首要经过 RX 引脚移入数据的最低有用位。该形式下,USART_DR 存放 器的缓冲区 (RDR) 坐落内部总线和接纳移位存放器之间。

进程:

1.经过向 USART_CR1 存放器中的 UE 位写入 1 使能 USART。

2. 对 USART_CR1 中的 M 位进行编程以界说字长。

3. 对 USART_CR2 中的间断位数量进行编程。

4. 假如将进行多缓冲区通讯,请挑选 USART_CR3 中的 DMA 使能 (DMAR)。依照多缓冲 区通讯中的解说阐明装备 DMA 存放器。进程 3

5. 运用波特率存放器 USART_BRR 挑选所需波特率

6. 将 RE 位 USART_CR1 置 1。这一操作将使能接纳器开端查找开端位。

接纳到字符时

● RXNE 方位 1。这表明移位存放器的内容已传送到 RDR。也就是说,已接纳到并可读取数据(以及其相应的过错标志)。

● 假如 RXNEIE 方位 1,则会生成间断。

● 假如接纳期间已检测到帧过错、噪声过错或上溢过错,过错标志位可置 1。

● 在多缓冲区形式下,每接纳到一个字节后 RXNE 均置 1,然后经过 DMA 对数据存放器履行读操作清零。

● 在单缓冲区形式下,经过软件对 USART_DR 存放器履行读操作将 RXNE 位清零。RXNE标志也能够经过向该位写入零来清零。RXNE 位有必要在完毕接纳下一个字符前清零,以防止发生上溢过错。

留意:接纳数据时,不该将 RE 位复位。假如接纳期间制止了 RE 位,则会间断接纳当时字节。

间断字符

接纳到间断字符时,USART 将会依照帧过错对其进行处理。

闲暇字符

检测到闲暇帧时,处理进程与接纳到数据的状况相同;假如 IDLEIE 位为 1,则会发生间断。

上溢过错

假如在 RXNE 未复位时接纳到字符,则会发生上溢过错。RXNE 位清零前,数据无法从移位 存放器传送到 RDR 存放器。

每接纳到一个字节后,RXNE 标志位都将置 1。当 RXNE 标志位是 1 时,假如在接纳到下一 个数据或没有处理上一个 DMA 恳求时,则会发生上溢过错。发生上溢过错时: ● ORE 方位 1。

● RDR 中的内容不会丢掉。对 USART_DR 履行读操作时可运用从前的数据。

● 移位存放器将被掩盖。之后,上溢期间接纳到的任何数据都将丢掉。

● 假如 RXNEIE 方位 1 或 EIE 与 DMAR 位均为 1,则会生成间断。

● 经过先后对 USART_SR 存放器和 USART_DR 存放器履行读操作将 ORE 位铲除。

留意:ORE 方位 1 时表明至少 1 个数据丢掉。存在两种或许:

● 假如 RXNE=1,则最终一个有用数据存储于接纳存放器 RDR 中而且可进行读取;

● 假如 RXNE=0,则表明最终一个有用数据已被读取,因而 RDR 中没有要读取的数据。接纳到新(丢掉)数据的一起已读取 RDR中的最终一个有用数据时,会发生该状况。读取序列期间(在 USART_SR 存放器读拜访与 USART_DR 读拜访之间)接纳到新数据时也会发生该状况。

挑选适宜的过采样办法

接纳器选用不同的用户可装备过采样技能(除了同步形式下),能够从噪声中提取有用数据。

可经过编程 USART_CR1 存放器中的 OVER8 位来挑选采样办法,且采样时钟能够是波特率 时钟的 16 倍或 8 倍。

依据使用:

● 挑选 8 倍过采样 (OVER8=1) 以取得更高的速度(高达 fPCLK/8)。这种状况下接纳器对时钟误差的最大容差将会下降。

● 挑选 16 倍过采样 (OVER8=0) 以添加接纳器对时钟误差的容差。这种状况下,最大速度限制为最高 fPCLK/16可经过编程 USART_CR3 存放器中的 ONEBIT 位挑选用于评价逻辑电平的办法。有两种挑选:

● 在已接纳位的中心进行三次采样,然后进行大都表决。这种状况下,假如用于大都表决的 3 次采样成果不相等,NF 方位 1。

● 在已接纳位的中心进行单次采样

依据使用:

— 在噪声环境下作业时,请挑选三次采样的大都表决法 (ONEBIT=0);在检测到噪声时请回绝数据,由于这表明采样进程中发生了搅扰。

— 线路无噪声时请挑选单次采样法 (ONEBIT=1) 以添加接纳器对时钟误差的容差。这种状况下NF 位一直不会置 1。

帧中检测到噪声时:

● 在 RXNE 位的上升沿时 NF 方位 1。

● 无效数据从移位存放器传送到 USART_DR 存放器。

● 单字节通讯时无间断发生。但是,在 RXNE 位发生间断时,该位呈现上升沿。多缓冲区通讯时,USART_CR3 存放器中的 EIE 方位 1 时将宣布间断。

经过先后对 USART_SR 存放器和 USART_DR 存放器履行读操作将 NF 位清零。

留意:智能卡、IrDA 和 LIN 形式下不可选用 8 倍过采样。在这些形式下,OVER8 位由硬件强制 清零。