根据雷达(RADAR)和开麦拉规划的运用正大举进驻轿车驾驭安全范畴。开始,自习惯巡航操控和路途违背警报等先进驾驭辅佐体系(ADAS)仅仅一些十分便当的功用,而现在,它们在车辆操控上扮演更积极主动的人物,支撑完结车道保持辅佐(LKA)等功用。曾经的高功用中央处理器(CPU)被以为是最适合这些运用的组件,但车厂需求归纳考虑运算功用和低功率耗费,这促进工程师转向选用现场可编程门阵列(FPGA)组件。

ADAS需求满意特其他功用安全要求。在2011年,ISO发布针对载重3.5吨以下客车的ISO26262标准,以下降体系呈现毛病后形成危险的危险。这个标准要求选用紧密的规划进程,在运用履行进程中勘探随机硬件毛病,以削减体系性毛病。

进步ADAS功用安全 FPGA SoC受喜爱

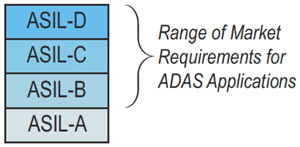

运用开发人员界说了专门的安全方针,针对每个方针分配相应的轿车安全完整性等级(ASIL)。关于运用中最高档其他ASIL-D,一般界说了每一个组件从开发直至运作到寿数终了时应满意的要求。图1显现了从客户需求视点来看,ADAS应契合的ASIL现在的规模。

图1 ADAS所需ASIL标准等级

ASIL-B是市场上的最低等级,而某些运用则要求选用ASIL-D,以支撑某些功用。越来越多的ADAS运用对ASIL有更严厉的要求。在某些详细完结中,组件的通用ASIL或许项目(体系)等级都会带来不必要的复杂度,影响开发本钱和进展。剖析体系概念,得出安全概念和要求后,还可以把运用分红几种不同的过程,具有不同的ASIL,如此一来,体系规划则可更简单完结,并且完结的功率更高。

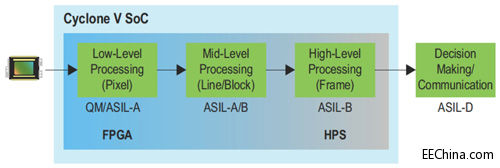

例如,前方开麦拉运用运用ADAS中常见的一个印象传感器,如图2显现的高阶结构图。一个印象传感器衔接至图画处理器,该处理器可以是Altera Cyclone FPGA体系单芯片(SoC)或其他计划。信号处理链路和数据流被分红四个部分。首要,透过把印象变换成更有用的表现方式,在像素层级上进行底层处理。然后,对印象或许区块图画进行中心层级处理,运用相应的算法,提取出边际等特征。下一步,则会进行高阶处理,提取出每一个图帧的数据,勘探方针并进行分类。然后,体系会追寻方针,假如需求采纳办法,则与煞车或许转向引擎操控单元(ECU)进行通讯。

图2 高阶单一前方开麦拉ADAS

除了可以在FPGA上十分高功率的完结底层和中心层级处理,用户也可以在Cyclone V系列FPGA SoC硬式中心处理器体系(HPS)的Cortex-A9等处理中心完结某些中心层级处理。高阶处理主要是句柄,可以映像到HPS中的一个或许两个Cortex-A9上。处理链路的终究一步是方针追寻和判别,可以在外部微操控器(MCU)上完结这一个过程。

在整个处理进程中,工程师可将输入数据进行简化,以得到更有意义的数据,数据削减意味进步安全临界值。因而,底层完结可以分红质量办理(QM)或底层ASIL(例如ASIL-A)。会这样做的原因是因为单一个像素期间呈现的毛病对后续算法的功用影响很小,因而可以疏忽。在这个比如中,假定中心层级处理契合ASIL-A或ASIL-B,辨认方针并进行分类的高阶处理功用应契合ASIL-B。对方针进行分类后,会发生方针表,并供给应微操控器,进行方针追寻和判别。这是信号链路最要害的部分,咱们以为它应该契合ASIL-D,这对轿车的行为有直接影响。

完结分级安全处理 FPGA统筹规划牢靠度/功率

在这类运用中,最好对数据流进行更全面的剖析,每一个层级的安全临界界说对整个体系的功用会发生直接影响。对前面运算层级有太高的安全要求会导致难以满意体系功用方针,并且对体系全体安全的影响很小。不过,处理链路底层也会呈现毛病,对体系安全功用发生较大的影响,例如,底层处理功用的永久毛病会导致高层上的数据永久危害,透过合理性查看很简单勘探到这类毛病,对体系功用的影响相对较小。

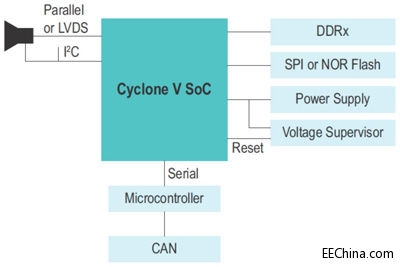

图3显现单一前方摄像机体系实例的高阶结构图。由一个外部电源办理电路为Cyclone V SoC供给电源,当供电电压不在额外运作规模内时,独自的电压监控功用会发生重置,外部非挥发性内存衔接至四路串行周边接口(Quad SPI)模块,体系启动进程中加载运用程序,装备FPGA时会运用这些模块。咱们运用双倍数据率(DDR)内存来履行运用程序代码、贮存数据和印象图帧,透过SPI衔接外部微操控器,进行方针勘探和终究判别,并运用操控器局域网络(CAN)接口与轿车底盘的其他部分进行通讯。

图3 单一前方开麦拉体系实例

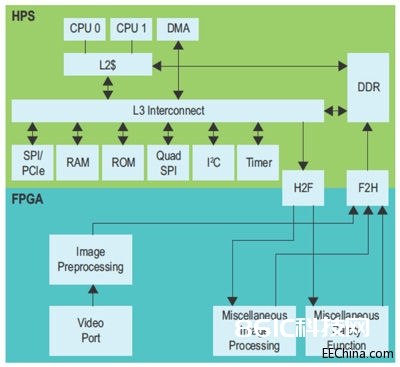

此运用所运用的图画处理器模块如图4所示。视讯端口接纳来自印象传感器的数据,将其传送至图画处理模块,这一个模块相当于底层图画处理层级,在这个比如中,数据透过图画处理模块后,经过FPGA至HPS(F2H)桥接被写入到DDR内存中,也可以传送至下一层级,完结的功率更高。第二级是中心层级处理,由各种图画处理模块来完结,透过HPS至FPGA(H2F)桥接读出曾经贮存在DDR内存中的数据,再次将其写入到DDR内存中。在这个比如中,由HPS完结高阶处理层级。

图4 Cyclone V SoC电路架构图

发挥可编程效益 FPGA全方位勘探体系毛病

接下来的阶段将阐明用于勘探规划中,不同区域是否有毛病的确诊功用。一些确诊功用可以勘探到永久毛病,而有的只能勘探到暂时性毛病,也有的能勘探各种毛病。暂时性毛病是一种呈现后又消失的毛病,关于这一类景象,规划人员应考虑完结某些功用时内存中呈现的毛病,以及完结功用时逻辑中或许呈现的毛病。

在运用软件运用印象传感器之前,工程师应对其进行装备,在运用程序履行进程中不断修正装备以习惯不同的光线条件。印象传感器关于运用操作十分要害,因而,主张在容错时刻距离(FTTI)期间对其装备至少进行一次查看,这并不一定能掩盖传感器一切或许的毛病,但可以办理好装备缓存器组(表1)。