许多现代工业和仪器仪表体系能够接入多个不同电源,最常见的是15 V用于模仿电路,3 V或5 V用于数字逻辑。其间大部分运用要求输出以10 V摆幅驱动外部大负载。本文评论为这些运用挑选数模转化器(DAC)时遇到的各种权衡要素,而且提出了具体的电路原理图。

可编程逻辑操控器(PLC)、进程操控或电机操控等工业运用中的模仿输出体系,需求0 V至10 V或10 V以上的单极性或双极性电压摆幅。一种或许的解决计划是挑选能够直接发生所需输出电压的双极性输出DAC。还有一种解决计划是运用低压单电源(LVSS)DAC,将其输出电压扩大至所需输出电平。为了挑选最适合运用的办法,用户有必要了解输出要求,而且知道每种计划的优势或缺乏。

能够直接发生所需输出摆幅的双极性DAC具有多项值得考虑的优势和缺乏。首要优势包含:

* 简略。电路板的规划得以简化,由于所需的0 V至10 V或10 V以上输出电平可直接经过硬件或软件装备取得。此外,其一般会集成毛病维护模式,因而可简化体系规划。

* 可制作性和可靠性得到前进,由于不需求扩大器 、开关和电阻等分立式器材。有时也会集成基准电压源。

、开关和电阻等分立式器材。有时也会集成基准电压源。

* 体系差错和总非调整差错(TUE)的丈量。确保线性度、噪声、失谐和漂移特性;对DAC内的各种差错源求和,很简略核算整体系差错或TUE。TUE有时在数据手册中有规则。

* 端点差错。某些状况下,双极性DAC包含校准特性,能够随时调整体系失谐和增益差错。

双极性DAC的首要缺陷包含:

* 灵活性有限。集成高压扩大器 对运用而言或许不是最佳的。输出扩大器

对运用而言或许不是最佳的。输出扩大器 一般针对特定负载和噪声要求进行优化。尽管数据手册给出的规模或许与体系中的实践负载匹配,但其他参数(如树立时刻或功耗等)或许无法满意体系要求。

一般针对特定负载和噪声要求进行优化。尽管数据手册给出的规模或许与体系中的实践负载匹配,但其他参数(如树立时刻或功耗等)或许无法满意体系要求。

* 本钱和电路板面积。双极性DAC一般是在较大的几许工艺上规划,导致芯片和封装尺度较大且本钱较高。

运用带外部信号调度的低压DAC是另一种发生工业运用所需高压输出摆幅和规模的办法。相同,它也有值得考虑的重要权衡要素。分立式解决计划的首要优势包含:

* LVSS DAC往往具有较高的逻辑集成度和高速逻辑接口,使得微操控器有时刻来处理更多使命。

* 输出或许有必要供给大电流或驱动双极性DAC片内扩大器 无法处理的大容性负载。分立式解决计划答应挑选最佳独立扩大器

无法处理的大容性负载。分立式解决计划答应挑选最佳独立扩大器 来满意运用需求。

来满意运用需求。

* 很简略完成超量程特性(10 V标称规模供给10.8 V输出),为最终用户供给更大的运用灵活性,例如在需求翻开或封闭磨损阀门的运用中。

* 本钱。LVSS DAC一般比双极性DAC廉价,从而使整体物料本钱更低。

* 削减电路板面积。LVSS DAC选用低压亚微米或深微米工艺规划,可供给小尺度封装。

分立式解决计划的首要缺陷包含:

* 需求花费更多的时刻来优化电路板和规划端点调整电路。

* 总差错或TUE的核算变得更困难,由于有必要考虑更多差错源。

* 分立式器材数量的添加导致可制作性和可靠性下降。

* 运用有必要有低压电源(5 V或3 V)可用。

总归,在精细10 V工业运用的规划中,有许多要素需求考虑。明显,规划人员有必要清楚地知道输出负载要求和体系能够承受的总差错。此外,电路板面积和本钱也是挑选最佳计划的重要考虑要素。关于有必要驱动大容性负载(1 μF),一起要求低噪声和快速树立(20 V规模小于10 s)的运用,分立式计划简直总是胜出。尽管双极性DAC在灵活性上不如分立式计划,但简略的规划和不吃力的TUE核算使其对广泛的工业和仪器仪表运用很有吸引力。

下面的评论阐明怎么使用双电源双极性输出DAC和带外部信号调度的低压单电源DAC完成精细10 V输出。

电路概览:双电源双极性输出DAC

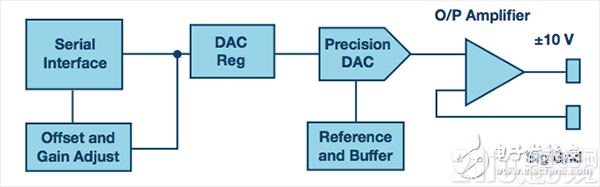

图1. AD5764双极性DAC的功用框图

双极性输出DAC的首要元件如以上功用框图(图1)所示。它由精细DAC、基准电压源、基准电压缓冲器、失谐和增益调整以及输出扩大器组成。集成精细基准电压源以习惯16位运用十分困难,但最近的工艺前进和规划技能答应在片内规划和集成具有超卓漂移和热特性的基准电压源。热关断、短路维护等毛病维护模式,以及上电/关断等状况下的输出操控,是双极性DAC一般会集成的重要特性,能够简化体系规划。DAC供给数字码以相关于基准电压转化输出电压。调整模块供给偏移和调整DAC传递函数的功用。

有关AD5764的更多信息

AD5764是一款四通道、16位串行输入、电压输出DAC,作业电压规模为12 V至15 V。其标称满量程输出规模为10 V,内置输出扩大器、基准电压缓冲器、精细基准电压源以及专有上电/关断操控电路。AD5764选用ADI公司的工业CMOS (iCMOS?)制作工艺技能规划,该工艺集高压互补双极性晶体管和亚微米CMOS于一体。它还有一个模仿温度传感器,每通道均有对应的数字失谐和增益调整寄存器。

电路概览:低压单电源DAC和外部信号调度

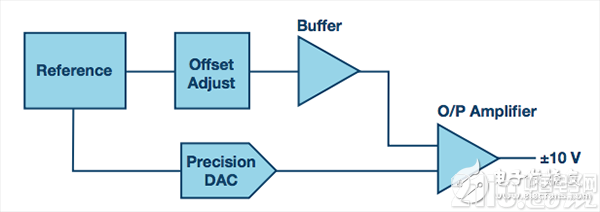

图2显现怎么使用LVSS DAC发生工业运用所需的10 V输出规模。它由5个不同的模块组成:LVSS DAC、基准电压源、失调调整、基准电压缓冲器和输出扩大器。

图2. 分立式±10 V模仿输出框图

DAC供给数字码以相关于基准电压转化输出电压。失调调整模块供给偏移DAC单极性传递函数以发生双极性输出的功用,以及校准0 V端点的功用。基准电压缓冲器为基准电压和失调调整模块供给负载阻隔(多个DAC可共用这一缓冲输出)。输出扩大器在计入失调调整后,供给所需的增益来将输出摆幅前进到所需电平。此外,输出扩大器还供给将大容性负载驱动到供电轨的功用。

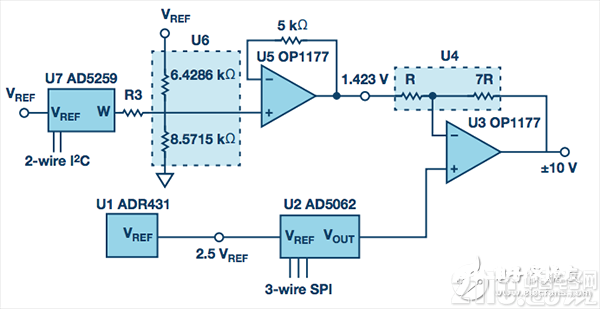

图3所示电路阐明了怎么扩大一个精细LVSS 16位DAC来完成10 V的输出摆幅。DAC具有0到2.5 V输出规模,连接到扩大器U3的同相输入端。此输入的同相增益为(1 + R2/R1),本例中为8。运算扩大器的反相输入端连接到基准电压源和电阻分压器网络U6发生的1.429 V电压。此输入的反相增益为(–R2/R1),本例中为–7。因而,当DAC设为0代码0000h时,此电路的输出为:

(0/65535 2.5 8) – (7 1.429 V) = –10 V.

当DAC设置为满量程代码FFFFh时,输出为:

(65535/65535 2.5 8) – (7 1.429 V) = +10 V.

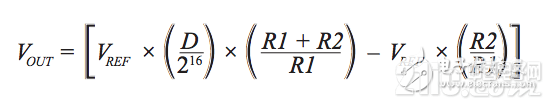

一般来说,恣意输入代码的输出电压能够按如下公式核算:

其间D代表精细16位DAC(好像本例)的十进制输入代码(0至65535)。VREF = 2.5 V,R1 = R,R2 = 7 R。使用一个带非易失性存储器的数字电位计来调整体系的零失调差错,这样即便断电也能保存失调值。能够挑选U7、U6和R3来构成电阻网络,以便供给0 V所需的调整规模。能够轻松进行装备PLC模仿输出模块所需的其他输出规模,例如+5 V、5 V、+10 V或10.8 V (适用于超量程较为重要的状况)。

图 3. 10 V精细模仿输出电路概况

该电路包含如下器材:U1—ADR421,精细、低噪声2.5 V基准电压源,3 ppm/°C漂移,MSOP封装;U2—AD5062,16位、最大1 LSBINL、5 V/3 V电源、串行输入nanoDAC,SOT-23封装;U3和U5—OP1177,精细运算扩大器,15 V电源,MSOP封装;U4和U6—带ESD维护的精细电阻网络;U7—AD5259,256抽头非易失性数字电位计,MSOP封装。

有关AD5062的更多信息16位AD5062确保单调性,最大DNL和INL差错为1 LSB。其单极性输出的最大失调差错为50 V,最大增益差错为0.02%。高速串行接口支撑高达30 MHz的时钟速率。 该器材选用SOT-23小型封装。