一、前语

FPGA在电子商场上占有无足轻重的位置。现在的问题是:现在商场在FPGA开发方面的EDA东西令人目不暇接,各自侧要点不同,功用也不相同,咱们应该怎么挑选?为了加快FPGA的开发,挑选并协调好各种EDA东西显得十分重要,本文将讨论上述问题并给出一种解决方案。本文以Altera公司的FPGA为方针器材,经过开发实例介绍FPGA开发的完好的流程及开发进程中运用到的开发东西,包含QuartusII、FPGA CompilerII、Modelsim,偏要点阐明怎么运用这三个东西进行协同规划。

二、FPGA的开发流程及实例

FPGA的开发分为规划输入、功用仿真、规划归纳、前仿真、布局布线、时序仿真、时序剖析和编程下载几个进程。规划流程如图1所示。

咱们的开发实例是“带次第挑选和奇偶查验的串并数据转化接口”。接口电路能够完结数据的串并转化,并依据操控信号确认输出的并行数据的次第,以及输出奇偶查验位。开发实例是用来阐明FPGA的开发流程和各种EDA东西的协同规划,因而这儿的描绘要点并在规划自身。开发实例运用的方针器材是Altera公司FLEX10KE系列的EPF10K30ETC114-1;开发软件有QuartusII2.0、FPGA CompilerII 3.6和Modelsim5.6SE。

Quartus II是Altera公司的第四代可编程逻辑器材集成开发环境,供给从规划输入到器材编程的悉数功用。 Quartus II能够发生并辨认EDIF网表文件、VHDL网表文件和Verilog HDL网表文件,为其他EDA东西供给了便利的接口;能够在Quartus II集成环境中主动运转其他EDA东西。

Mentor Graphics公司的Modelsim是业界较好的仿真东西,其仿真功用强大,且图形化界面友爱,并且具有结构、信号、波形、进程、数据流等窗口。

FPGA Compiler II是一个完善的FPGA逻辑剖析、归纳和优化东西,它从HDL方式未优化的网表中发生优化的网表文件,包含剖析、归纳和优化三个进程。

假如规划的硬件体系不是很大,对归纳和仿真的要求不是很高,咱们完全能够在Quartus II中完结规划。实践上,这个开发实例完全能够在Quartus II这个集成的开发环境中完结。下面,我先介绍一下怎么在Quartus II中完结规划,然后再介绍怎么运用Quartus II供给的第三方EDA东西的接口与其他EDA东西(包含归纳东西FPGA Compiler II和仿真东西ModelSim5.6SE)完结协同规划。

1. 依据Quartus II的FPGA的开发

运用Quartus II软件的开发流程可归纳为以下几步:规划输入、规划编译、规划时序剖析、规划仿真和器材编程。

(1)规划输入

Quartus II软件在File菜单中供给“New Project Wizard…”导游,引导规划者完结项目的创立。当规划者需求向项目中增加新的VHDL文件时,能够经过“New”选项挑选增加。在这儿咱们创立项目“s_to_p”,编写“s_to_p.vhd文件”,并将文件增加到项目中。

(2)规划编译

Quartus II编译器完结的功用有:检查规划过错、对逻辑进行归纳、提取守时信息、在指定的Altera系列器材中进行适配切割,发生的输出文件将用于规划仿真、守时剖析及器材编程。

①首要确认软件处于Compile Mode,能够经过Processing菜单进行挑选。

②在Processing菜单中挑选Compiler Settings项。在这儿能够进行器材挑选、形式设定、归纳和适配选项设定及规划验证等。咱们挑选FLEX10KE系列型号为EPF10K30ETC114-1的器材,并挑选在编译后进行时序剖析。

③单击Processing菜单下的“Start Compilation”项,开端编译进程。

④检查编译成果。编译成果以树状结构安排在Compilation Report中,包含项目的设置信息,以及编译设置、编译作用等信息,一起也包含了静态时序信息。

(3)规划守时剖析

单击Project菜单下的“Timing Settings…”选项,能够便利地完结时刻参数的设定。Quartus II软件的时序剖析功用在编译进程完毕之后主动运转,并在编译陈述的Timing Analyses文件夹中显现。其间咱们能够得到最高频率fmax、输入寄存器的树立时刻tsu、输出寄存器时钟到输出的推迟tco和输入坚持时刻th等时刻参数的具体陈述,从中能够清楚地断定是否到达体系的时序要求。本规划实例电路的fmax可到达192.31MHz。

(4)规划仿真

Quartus II软件答应规划者运用依据文本的向量文件(.vec)作为仿真器的鼓励,也能够在Quartus II软件的波形修改器中发生向量波形文件(.vwf)作为仿真器的鼓励。经过Quartus II的波形修改器,咱们修改波形文件“s_to_p.vwf”用于仿真。接着,在Processing菜单下挑选“Simulate Mode”选项进入仿真形式,挑选“Simulator Settings…”对话框进行仿真设置。在这儿能够挑选鼓励文件、仿真形式(功用仿真或时序仿真)等,咱们挑选时序仿真,单击“Run Simulator”即开端仿真进程。完结仿真后,咱们能够经过时序仿真得到的波形判别体系规划是否到达要求。

(5)器材编程

规划者能够将装备数据经过MasterBlaster或ByteBlasterMV通讯电缆下载到器材傍边,经过被迫串行(Passive Serial)装备形式或JTAG形式对器材进行装备编程,还能够在JTAG形式下给多个器材进行编程。运用Quartus II软件给器材编程或装备时,首要需求翻开编程器(在New菜单选项中挑选翻开Chain Description File),在编程器中能够进行编程形式设置(Mode下拉框)、硬件装备(Programming Hardware对话框)及编程文件挑选(Add File…按钮),将以上装备存盘发生.cdf文件,其间存储了器材的称号、器材的规划及硬件设置等编程信息。当以上进程正确无误后,单击Start按钮即可开端对器材进行编程装备。这儿咱们需求依据外围硬件电路规划的状况进行挑选。

2.多种EDA东西协同规划

在FPGA规划的各个环节都有不同公司供给不同的EDA东西。每个EDA东西都有自己的特色。一般状况,由FPGA厂商供给的集成开发环境,如Quartus II,在规划归纳和规划仿真环节都不是十分优异,因而一般都会供给第三方EDA东西的接口,让用户更便利地运用其他EDA东西。在这方面,作为EDA集成开发环境的Quartus II做得很好,不只能够发生并辨认EDIF网表文件、VHDL网表文件和Verilog HDL网表文件,为其他EDA东西供给了便利的接口,并且能够在Quartus II集成环境中主动运转其他EDA东西。

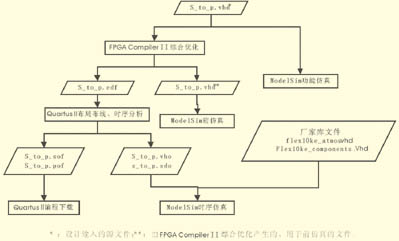

在FPGA的开发中,假如选用Altera公司器材的话,Quartus II+FPGA Compiler II+Modelsim的东西组合是十分抱负的挑选。如图2所示,运用这三个EDA东西对实例进行协同规划的流程。下面,咱们将具体介绍这三个东西的协同规划。

(1)规划输入和归纳

在FPGA Compiler II中修改“s_to_p.vhd”规划文件,并进行逻辑剖析、归纳和优化。运用FPGA Compiler II归纳时,咱们能够设置归纳的各种约束条件及优化要点,并挑选不同厂家的器材。在规划中,咱们运用File菜单中的“Design Wizard”,创立项目,增加“s_to_p.vhd”规划文件,并挑选Altera公司FLEX10KE系列型号为EPF10K30ETC114-1的器材为方针器材,在设置完结后,软件将主动开端归纳和优化。归纳、优化后,咱们能够检查成果和归纳所得到的原理图,看看是否能满足要求。接着,在Synthesis菜单中挑选“Export Netlist…”翻开导出网表的对话框。在这儿,能够设置和导出用于布局布线和前仿真的网表。在项目对应的文件夹中,“s_to_p.edf”是用于Quartus II布局布线的,而“s_to_p.vhd”(留意:这个文件和源文件具有相同的姓名)则用于Modelsim前仿真的。

(2)功用仿真和前仿真

运用Modelsim来进行功用仿真和前仿真。在Modelsim进行功用仿真和前仿真的操作一摸相同,仅仅输入的源程序不同算了。首要,咱们要创立项目,挑选对应的作业库,并将源文件参加到项目中。接着挑选Compile菜单中的“Compile…”对源文件进行编译,并编写测试台(能够是Macro文件,也能够是TestBench)。最终,挑选Simulate菜单中的“Simulate…”,在“Simulate”对话框中挑选仿真需求实体,选用对应的测试台进行仿真,验证体系的逻辑功用及归纳后的逻辑功用的正确性。

(3)布局布线和时序剖析

假如仿真成果没有问题,接下来的作业便是布局布线。在布局布线之前,先对Quartus II的规划环境进行设置。在Project菜单中挑选“EDA Tool Setting…”,翻开EDA东西设置对话框。在这儿,咱们能挑选规划输入和归纳东西,仿真东西,时序剖析东西和地图级东西。现在,咱们关怀的是规划输入和归纳东西还有仿真东西,别离在对应的列表框中挑选FPGA Compiler II和Modelsim。留意仿真东西还要确认输出言语。布局布线的输入源文件是经FPGA Compiler II归纳、优化的输出文件。在这儿,FPGA Compiler II 的输出文件“s_to_p.edf”便是Quartus II布局布线的输入文件。对这个文件进行编译和时序剖析,就能够得到布局布线后的用于时序仿真和编程下载的文件。调查编译成果,发现时序剖析中fmax为204.08MHz,就这个方针而言,选用FPGA Compiler II归纳、优化明显比选用Quartus II归纳的作用要好。编译输出的文件中有几个是下面进程要用到的:一个是时序仿真文件,软件将这些文件都存于项目文件夹下面的“Simulation”文件夹中,包含描绘电路的逻辑结构的网表文件“s_to_p.vho”和对应的延时规范格局文件“s_to_p_vhd.sdo”;另一个是编程下载文件,包含不同格局的“s_to_p.sof”和“s_to_p.pof”。

(4)时序仿真

进行时序仿真前,咱们要确认现已取得针对特定FPGA输出网表文件,对应延时规范格局文件,以及厂家供给的与特定FPGA对应的库文件。其间网表文件和规范延时格局文件是布局布线时发生的文件,而库文件则是由厂商供给,在Quartus II软件的装置目录中能够找到。本规划中,网表文件时“s_to_p.vho”,延时规范格局文件是“s_to_p_vhd.sdo”,并因为选用Altera公司FLEX10KE系列的EPF10K30ETC114-1为方针器材,所以库文件是“FLEX10KE_ATOMS.VHD”和“FLEX10KE_COMPONENTS.VHD”。 确认输入文件后,咱们就能运用Modelsim进行时序仿真。

首要,树立项目,将上述文件增加到项目中去,并在“work”库中新建 “flex10ke” 库。

接着,翻开“Compile”对话框,先在“flex10ke” 库中编译文件“flex10ke _atoms.vhd”和“flex10ke _compomnets.vhd”,再在“work”库中编译文件“s_to_p.vho”(留意一定要弄清楚编译次第)。

编译完结之后,咱们就能够进行仿真了。时序仿真与功用仿真和前仿真不同的是时序仿真需求参加延时规范格局文件。翻开“Simulate”对话框,挑选要仿真的实体“s_to_p”,并在挑选SDF标签,参加延时规范格局文件是“s_to_p_vhd.sdo”。其他的操作和功用仿真和前仿真相同。从时序仿真的成果,咱们能够进行最接近硬件的一次规划验证。

(5)编程下载

运用集成开发环境Quartus II中的编程东西,依据外围硬件电路的状况,设置编程形式,咱们能很便利地完结编程下载作业,在硬件上对规划进行验证。

三、定论

在实践的FPGA的开发中,选用Quartus II+FPGA Compiler II+Modelsim的EDA东西组合能很好地规划规划流程,充分运用各EDA东西的长处,进步开发功率。

参考文献

1 石俊斌,林辉.在PLD开发中进步VHDL的归纳质量,单片机与嵌入式体系使用,2003年,第4期

2 孙富明,李笑盈.依据多种EDA东西的FPGA规划,电子技术使用,2002年1月,第1期

3 林敏,方颖立.VHDL数字体系规划与高层归纳. 北京,电子工业出版社,2002年1月,12~61

4 Altera Corporation,“QuartusII Help Version 2.0”.

5 Model Technology Incorporated,“ModelSim SE User’s Manual Version 5.6”

6 Synopsys Incorporated,“FPGA Compiler II/FPGA Express VHDL Reference Manual Version 1999,05”