1、体系作业时钟频率

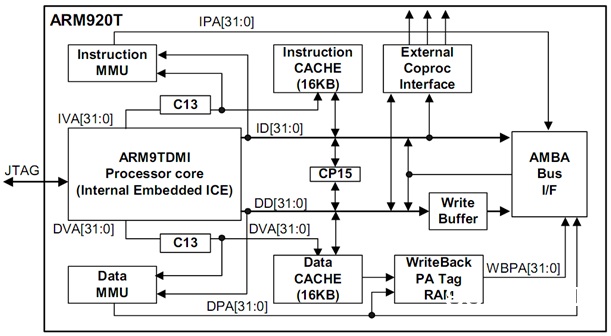

在对体系时钟进行提速之前,让我们先来了解下S3C2440上的作业时钟频率,FCLK,HCLK,PCLK,其间FCLK首要为ARM920T内核供给作业频率,如图2-44所示:

图2-44 ARM920T内核结构

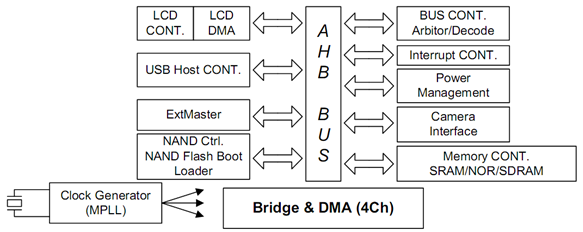

HCLK首要为S3C2440 AHB总线(Advanced High performance Bus)上挂接硬件供给作业频率,AHB总线首要挂接有内存,NAND,LCD操控器等硬件,如图2-45所示:

图2-45 S3C2440 AHB总线上挂接硬件

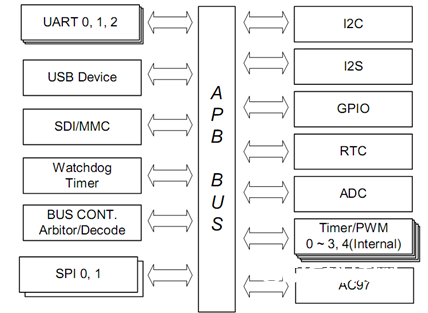

PCLK首要为APB总线供给作业频率,由图2-46所示,APB总线首要挂接UART串口,Watchdog等硬件操控器。

图2-46 S3C2440 APB总线挂接硬件

也就是说,关于一些需求时钟作业的硬件,假如堵截其时钟源 ,就不会再作业,然后到达降低功耗的意图,这也是便携嵌入式设备里的一个特色。

时钟源:为了削减外界环境对开发板电磁搅扰,下降制造本钱,一般开发板的外部晶振时钟频率都很低,MINI2440开发板由12MHz的晶振来供给时钟源,要想让CPU运转在更高的频率就要经过时钟操控逻辑单元PLL(锁相环)来进步主频。

S3C2440里有两个PLL:MPLL和UPLL,MPLL用来发生FCLK,HCLK,PCLK的高频作业时钟,UPLL用来为USB供给作业频率。

图2-47体系时钟初始化时序

开发板上电后,晶振OSC开端供给晶振时钟,因为体系刚刚上电,电压信号等都还不安稳,这时复位信号(nRESET)拉低,这时MPLL尽管默许发动,可是假如不向MPLLCON中写入值,那么外部晶振则直接作为体系时钟FCLK,过几毫秒后,复位信号上拉,CPU开端取指运转,这时能够经过代码设置发动MPLL,MPLL发动需求必定确定时刻(LockTime),这是因为MPLL输出频率还没有安稳,在这期间FCLK都中止输出,CPU中止作业,过了LockTime后时钟安稳输出,CPU作业在新设置的频率下,这时能够经过设置FCLK,HCLK和PCLK三者的频率份额来发生不同总线上需求的不同频率,下面具体介绍敞开MPLL的进程:

l 设置LockTime变频确定时刻

l 设置FCLK与晶振输入频率(Fin)的倍数

l 设置FCLK,HCLK,PCLK三者之间的份额

LockTime变频确定时刻由LOCKTIME寄存器(见下表)来设置,因为变频后开发板一切依靠时钟作业的硬件都需求一小段调整时刻,该时刻计数经过设置LOCKTIME寄存器[31:16]来设置UPLL(USB时钟锁相环)调整时刻,经过设置LOCKTIME寄存器 [15:0]设置MPLL调整时刻,这两个调整时刻数值一般用其默许值即可。

表2-8变频确定时刻寄存器(LOCKTIME)

|

寄存器名 |

地址 |

是否读写 |

描绘 |

复位默许值 |

|

LOCKTIME |

0x4C000000 |

R/W |

变频确定时刻寄存器 |

0xFFFFFFFF |

|

LOCKTIME |

位 |

描绘 |

初始值 |

|

U_TIME |

[31:16] |

UPLL对UCLK的确定时刻值 (U_TIME:300us) |

0xFFFF |

|

M_TIME |

[15:0] |

MPLL关于FCLK,HCLK,PCLK的确定时刻值(M_TIME:300us) |

0xFFFF |

FCLK与Fin的倍数经过MPLLCON寄存器设置,三者之前有以下联系:

MPLL(FCLK) = (2*m*Fin)/(p*2^s)

其间:m = MDIV + 8, p = PDIV + 2, s = SDIV

当设置完MPLL之后,就会主动进入LockTime变频确定期间,LockTime之后,MPLL输出安稳时钟频率。

表2-9 MPLL装备寄存器(MPLLCON)

|

寄存器名 |

地址 |

是否读写 |

描绘 |

复位默许值 |

|

MPLLCON |

0x4C000004 |

R/W |

MPLL装备寄存器 |

0x00096030 |

|

MPLLCON |

位 |

描绘 |

初始值 |

|

MDIV |

[19:12] |

主分频器操控位 |

0x96 |

|

PDIV |

[9:4] |

预分频器操控位 |

0x03 |

|

SDIV |

[1:0] |

后分频器操控位 |

0x0 |

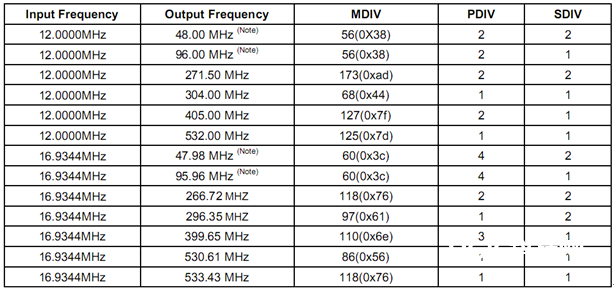

经过上述算法比较难以找到适宜的PLL值,下表给出了官方引荐的一些MPLL参阅设置:

表2-10 官方引荐MPLL

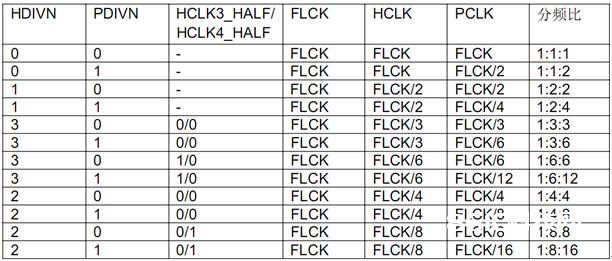

FCLK,HCLK,PCLK三者之间的份额经过CLKDIVN寄存器进行设置,S3C2440时钟设置时,还要额定设置CAMDIVN寄存器,如下表,HCLK4_HALF,HCLK3_HALF别离与CAMDIVN[9:8]对应,下表列出了各种时钟份额:

表2-11 FCLK HCLK PCLK设置份额

假如HDIV设置为非0,CPU的总线形式要进行改动,默许情况下FCLK = HCLK,CPU作业在fast bus mode快速总线形式下,HDIV设置为非0后, FCLK与HCLK不再持平,要将CPU改为asynchronous bus mod异步总线形式,能够经过下面的嵌入汇编代码完成:

__asm{

mrc p15, 0, r1, c1, c0, 0 /* 读取CP15 C1寄存器 */

orr r1, r1, #0xc0000000 /* 设置CPU总线形式 */

mcr p15, 0, r1, c1, c0, 0 /* 写回CP15 C1寄存器 */

}

关于mrc与mcr指令,请检查MMU与内存保护的完成章节。

表2-12时钟分频器操控寄存器(CLKDIVN)

|

寄存器名 |

地址 |

是否读写 |

描绘 |

复位默许值 |

|

CLKDIVN |

0x4C000014 |

R/W |

时钟分频器操控寄存器 |

0x00000000 |

|

CLKDIVN |

位 |

描绘 |

初始值 |

|

DIV_UPLL |

[3] |

UCLK挑选寄存器(UCLK有必要对USB供给48MHz) 0:UCLK=UPLL clock 1:UCLK=UPLL clock/2 |

0 |

|

HDIVN |

[2:1] |

00:HCLK = FCLK/1 01:HCLK = FCLK/2 10:HCLK = FCLK/4,当CAMIVN[9]=0 HCLK = FCLK/8,当CAMIVN[9]=1 11: HCLK = FCLK/3,当CAMIVN[8]=0 HCLK = FCLK/6,当CAMIVN[8]=1 |

0 |

|

PDIVN |

[0] |

0:PCLK是和HCLK/1相同时钟 1:PCLK是和HCLK/2相同时钟 |

0 |

表2-13摄像头时钟分频操控寄存器(CAMDIVN)

|

寄存器名 |

地址 |

是否读写 |

描绘 |

复位默许值 |

|

CAMDIVN |

0x4C000018 |

R/W |

摄像头时钟分频操控寄存器 |

0x00000000 |

|

CAMDIVN |

位 |

描绘 |

初始值 |

|

… |

… |

… |

… |

|

HCLK4_HALF |

[9] |

HDIVN分频因子挑选位(当CLKIVN[2:1]位为10b时有用) 0: HCLK=FCLK/4 1: HCLK=FCLK/8 |

0 |

|

HCLK3_HALF |

[8] |

HDIVN分频因子挑选位(当CLKIVN[2:1]位为11b时有用) 0: HCLK=FCLK/3 1: HCLK=FCLK/6 |

0 |

|

… |

… |

… |

… |