在高精度UWB定位体系中,方针信号是超短脉宽的脉冲,有很宽的带宽,为了对这种宽带信号进行处理,咱们要求如下两个条件。1)规划应该完成超高的采样率。关于UWB定位体系,康复较好的脉冲波形以取得较高时刻分辨率信息对错常有必要的,这就需求超高的采样率。等效采样率与信号重复频率和采样时钟有关。2)体系应该供给满意的模仿带宽来处理UWB信号以避免失真。

现有对UWB脉冲信号的采样办法有3种:直接采样、频域采样、次序欠采样。关于直接采样,因为每个ADC的输入信号带宽非常大,会导致ADC的采样坚持电路难于规划;ADC的采样成果受采样时钟颤动影响较大,因而采样时钟有必要到达较高的精确度;一起,当完成较高的等效采样率时,会需求较多的ADC,资源开支大。此外,当UWB体系遭到窄带信号搅扰时,就有必要进步时刻替换ADC的动态规模,来确保接纳机的功用。与直接采样比较,频域采样对时钟颤动则不灵敏。可是滤波器组规划杂乱。次序欠采样是经过两个参阅时钟振荡器来完成的。假定f0= 9.999 000 MHz,f0+△f=10 MHz,那么次序欠采样重构一个脉冲信号所需时刻为1 ms,能够到达的等效采样率为99.99 GHz。其与需求的距离为:重构信号所需时刻长,简单遭到时钟颤动的影响。

为了处理带宽与采样率这一对立,本文规划一款根据改换采样的UWB信号接纳机。经过超宽带盯梢坚持器(带宽为5 GHz)与低采样率的ADC(500MSPS)合作作业能够完成带宽为5 GHz,等效采样率最大为200 GHz的超宽带信号接纳。该技能将为别离载荷通讯与定位技能的完成供给有力的支撑。

1 总体规划

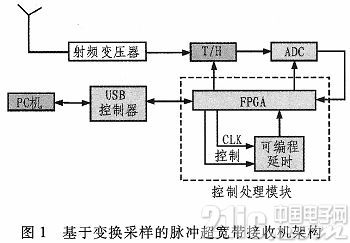

根据改换采样的脉冲式超宽带体系接纳机架构如图1所示。它包含一个盯梢坚持放大器、一个ADC和一个可编程延时芯片。实践的ADC有一个固有的带宽约束,这与ADC可到达的最高采样率有关。因为ADC的采样率相对较低,ADC的模仿带宽或许无法掩盖UWB脉冲的带宽。因而考虑在ADC之前放置一个采样坚持放大器(模仿带宽5 GHz)以对输入的带通讯号进行直接采样,可有效地将输入信号转化为ADC需求的低通频率。

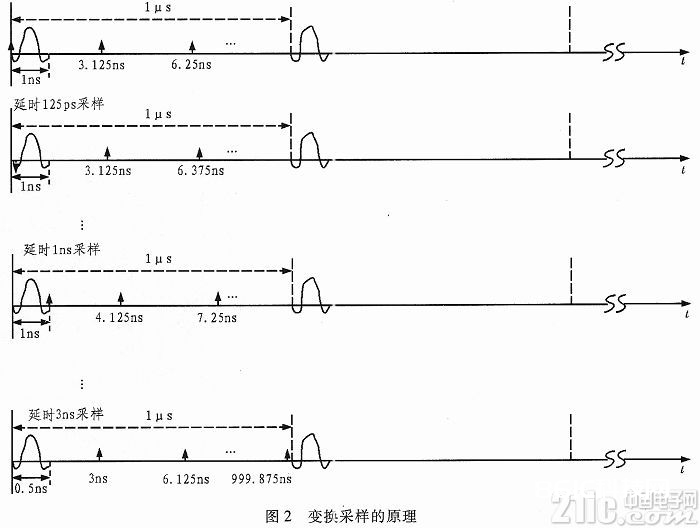

为了检测几百皮秒级(300 ps或3 GHz带宽)的窄脉冲,ADC的采样率至少为6 GS/s才干满意奈奎斯特原则,可是这样高功用的ADC在大多数的运用中要么是无法买到,要么是太贵重。文中致力于处理这个问题,经过采样时钟发生技能、高速ADC技能和数据拼接与处理技能来完成对UWB脉冲信号的无失真采样。超宽带体系接纳机架构中运用盯梢坚持器使改换采样器的模仿带宽到达了5 GHz,运用可编程延时芯片和低采样率的ADC即可等效完成8 GS/s的采样率。其原理框图如图2所示,横轴箭头对应的时刻为采样时刻。

发射的UWB信号重复频率为1 MHz,其脉冲重复时刻为1μs。所用的ADC采样率为320 MS/s,那么采样距离为3.125 ns,而UWB脉冲宽度为1 ns。ADC首要对第一个周期的脉冲进行采样,然后送入FPGA中存储,然后鄙人一个脉冲周期延时125 ps后再对UWB脉冲信号采样、存储;那么经过25个周期延时24次(每次延时以125 ps递加)即可得到25组样本值,每组样本选取40个采样值。运用数据拼接与处理技能,即可得到一个UWB脉冲周期的悉数信息,即可完成对脉宽为1ns的UWB信号的无失真采样。这样,等效采样距离为125 ps,即等效采样率为8 GS/s。这种采样办法就是以时刻资源为价值来获取8GS/S的等效采样率。

2 体系硬件规划

该体系分为4个部分:射频前端,ADC/时钟装备,数字硬件以及外部接口。

2.1 射频前端

射频前端包含单端转差分部分,以及盯梢坚持放大器。单端转差分部分运用ETC1-1-13TR传输线变压器进行转化,该变压器阻抗比为1:1,作业频率为4.5~3 000 MHz。为了扩展高速AD转化的模仿带宽以及高频线性度,在ADC之前加上HMC760LC4B盯梢坚持放大器。该放大器具有5 GHz的输入带宽,最大采样率为4 GS/s。为了在采样时钟到来之前盯梢坚持放大器坚持住数据,需求盯梢坚持放大器的采样时钟抢先ADC采样时钟一个时刻距离。

2.2 ADC/时钟装备

高速数据收集体系中,AD转化芯片是模仿和数字的转化中介,因而很大程度上决议了整个体系的功用。可是AD转化的功用很大程度上又遭到采样时钟的限制,传统的时钟电路都难供给高速ADC芯片所要求的低颤动、高速度的时钟。

本收集体系中ADC芯片ADS5463要求的采样时钟为320 MHz的高速差分时钟,差分方式为低电压伪发射极耦合逻辑电平LVPECL。因而,体系对采样时钟的颤动非常灵敏,而选用差分时钟能够比选用单端时钟有更好的噪声按捺功用,一起,选用差分时钟,能够减小时钟的颤动,进步SNR,然后取得更好的体系功用。本文运用FPGA内部的增强型PLL或许快速PLL对体系时钟倍频发生采样时钟,采样时钟最大为500 MHz。该体系选用改换采样的原理对UWB脉冲周期信号进行采样,需求在每一个脉冲重复周期内进行(等效采样率的倒数)的延时。延时芯片选用sy8929 7u,该芯片为双通道可编程延时线,每个通道的延时规模为2~7 ns,可编程延时增量为5 ps。延时改变根据串行可编程接口(SCLK,SDATA和SLOAD),每个通道的操控字为10 bit。为了添加延时,能够将多个sy89297u串联起来运用。

2.3 数字硬件

FPGA的并行性处理方式,使得FPGA成为高速ADC芯片高速数据流进行接纳、缓存处理的抱负计划,一起,这也是整个体系规划的要害。该体系选用芯片XC5VLX30—1FFG676I。该芯片array为,slice为4 800,最大可分配RAM为320 kb,最大高速I/O为400个,特别合适高速率大数据容量的处理。本文脉冲重复频率为1 MHz,AD的采样率为320MHz,那么在一个脉冲重复周期内将有320个采样点,可是因为一个周期内脉冲的占空比较小,为了减小资源的占用,下降数据率,在每个周期内只取那些有脉冲的采样点进行存储。在数据进行存储时,需求将数据进行拼接,然后再次序进行读取。为了下降数据的速率,还需求对数据进行非相干累加,这样就能够经过外部端口进行输出,在这里咱们选用USB端口与PC衔接,经过操控上位机,能够在电脑进步行数据的剖析。