1. 一般逻辑的复位

关于xilinx 7系列的FPGA而言,flip-flop支撑高有用的异步复/置位和同步复位/置位。对一般逻辑规划,同步复位和异步复位没有差异,当然因为器材内部信号均为高有用,因而引荐运用高有用的操控信号,最好运用高有用的同步复位。输入复位信号的低有用在顶层放置反相器能够被吸收到IOB中。

下面细说原因

先比较一下同步复位和异步复位的差异:

首先是同步复位,同步的操控信号包含同步置位/复位和使能,能够被吸收到LUT中,意图是为了防止操控集不同的LUT不能被归纳到同一个slice中,这样尽管进步了了LUT的运用率,却下降了slice的运用率,因小失大。

操控信号扇出不大于16的状况都能够尽或许的被吸收到同一个slice的LUT中去,在vivado中能够运用control_set_opt_threshold进行设置。

同步复位

always @(posedge I_sys_clk)

begin

if(I_rst)

begin

OUT1 《= 0;

end

else

begin

OUT1 《= &{a1,a2,a3,a4,a5,a6};

end

end

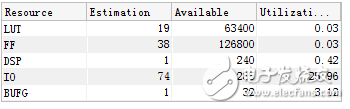

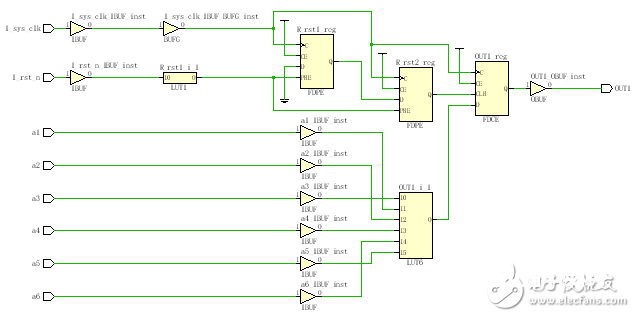

操控集优化为2时,能够看出复位信号中插入了LUT,可是因为在同一个slice中,运用形成的延时并不明显。留意关于扇出大的信号比方大局复位来说,这种操控集优化是不起作用的。

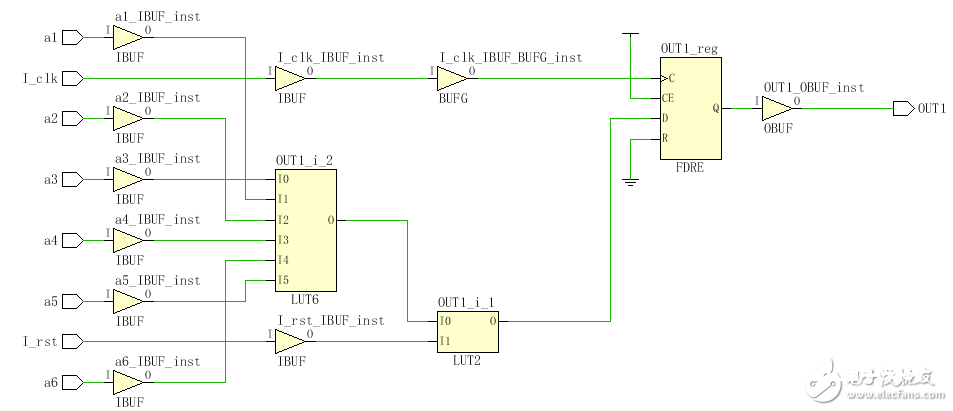

操控调集优化为0时,能够看出不会运用多于的LUT逻辑。

异步复位

always @(posedge I_sys_clk or posedge I_rst)

begin

if(I_rst)

begin

OUT1 《= 0;

end

else

begin

OUT1 《= &{a1,a2,a3,a4,a5,a6};

end

end

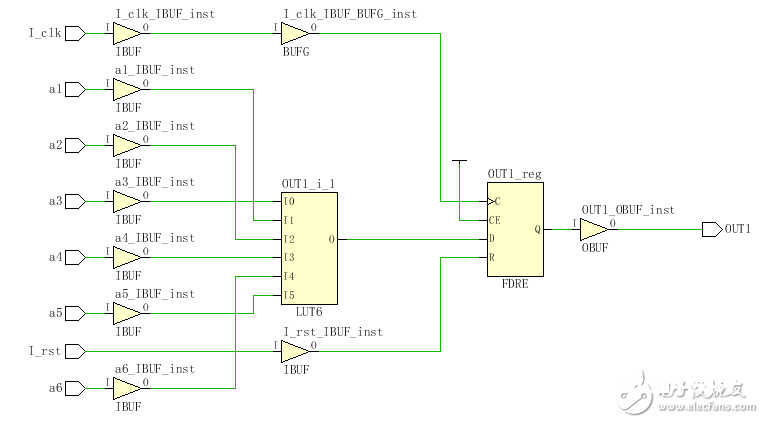

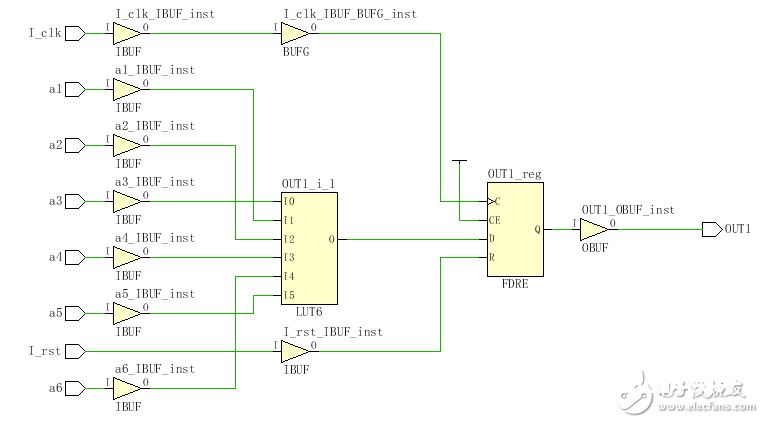

异步复位跟没有运用操控集归纳出的成果相同,能够看出不会运用额定的LUT逻辑。

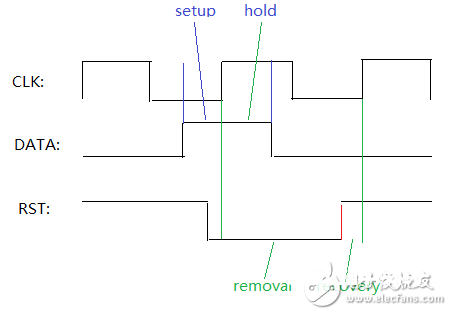

剖析Recovery/Removal

异步复位有Recover TIme 和Remove TIme 的危险,也就是说recovery TIme和removal TIme都是查看异步信号(reset或preset或set)的开释沿,开释沿必须在时钟沿前面提早recovery time开释,或许在时钟沿后removal time之后开释。

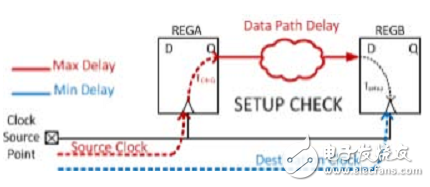

趁便简略剖析一下setup/hold,关于同一个时钟,必定满意data_path》clk_path,而hold的要求很小,所以必定满意。当data_path过长时,setup或许不满意。

假设不作同步的复位信号,那么recovery/removal都有或许不满意。

再考虑被本地时钟同步后的recovery/removal,同理复位信号对removal的时刻要求很小,同步后的复位信号的推迟就能满意removal。因为规划中的大局复位信号一般有很大的扇出,布线的延时会很严重,因而recovery的要求变得严厉。最好选用大局布线资源如BUFG,尽量用部分复位或许防止运用复位。

因而不管是同步复位仍是异步复位,都要运用同步后的复位信号。复位信号进来后先用本地时钟打两拍。在多个时钟域的时分留意是本地时钟,不是大局时钟。并在rtl中注明是异步存放器,使得归纳东西把简略同步器归纳在同一个slice中以削减延时,进步MTBF。

(* ASYNC_REG = “TRUE” *) (* keep = “true” *)reg system_reset_r;

(* ASYNC_REG = “TRUE” *) (* keep = “true” *)reg system_reset_r2;

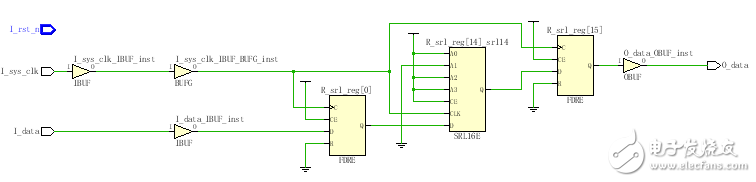

归纳的成果如图,同步化的异步复位。

2. 特别资源的复位

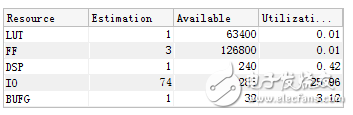

运用xilinx 原语SRL16、SRL32、LUTRAM

因为是运用LUT完结的上述功用,没有复位接口。只能依托 GSR方法来完结,不能运用复位。因而,在为以上这些资源编写代码时,应留意防止在编码中运用复位,以此来确保归纳东西归纳出相应的电路。

运用复位信号

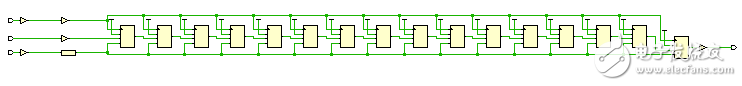

没有运用复位信号,能够看出归纳东西主动把输入和输出存放化,以满意更好的时序。

运用DSP48E1或BRAM

运用同步复位能够答应归纳东西运用 DSP48E1或BRAM等专用资源内部的存放器。这样能够改进规划中相应部分的器材整体运用率和功能,一起下降整体功耗。

下面以18X18的乘法器为例

同步复位

module multi_18x18(

input I_rst ,

input I_sys_clk ,

input [17:0]I_data1 ,

input [17:0]I_data2 ,

output reg [35:0] O_data

);

reg[17:0]R_data1,R_data2;

always @(posedge I_sys_clk)

begin

if(I_rst)

begin

R_data1 《= 18‘d0;

end

else

begin

R_data1 《= I_data1;

end

end

always @(posedge I_sys_clk)

begin

if(I_rst)

begin

R_data2 《= 18’d0;

end

else

begin

R_data2 《= I_data2;

end

end

always @(posedge I_sys_clk)

begin

if(I_rst)

begin

O_data 《= 36‘d0;

end

else

begin

O_data 《= R_data1*R_data2;

end

end

endmodule

异步复位,能够看出多运用了35个FF和18个LUT