作者:胡修林;席向涛;张蕴玉

跟着信息时代的到来,嵌入式体系成为继IT网络技能之后又一个新的技能发展方向。嵌入式体系以其功用强、体积小、功耗低、可靠性高以及面向职业运用的杰出特征,广泛运用于各个领域。

现场可编程门阵列FPGA(FieldProgrammableGateArray)是一种高密度可编程逻辑器材,其逻辑功用的完结是经过把规划生成的数据文件装备进芯片内部的静态装备数据存储器(SRAM)来完结的,具有可重复编程性,能够灵敏完结各种逻辑功用。FPGA的这种特性使其在现代电子体系规划中得到了广泛运用。依据SRAM工艺的FPGA是易失性的,体系掉电今后其内部装备数据将丢掉,因而需求外接ROM保存其装备数据。FPGA的装备是有时序要求的,假如FPGA自身不能操控装备时序,就需求有外部装备器材来进行时序操控。以Altera公司的系列FPGA为例,其自身不能操控装备时序,就有专用的EPC系列装备器材供其运用。在含有微处理器(MPU或MCU)的体系中(如嵌入式体系),能够运用微处理器发生装备时序,将保存在体系RO风吹草动的装备数据置入FPGA。与前面一种计划比较,该计划不只节省了本钱,更缩小了体系体积。在对本钱和体积灵敏的体系中,该计划十分适用。

在某手持式通讯设备的规划中,运用了嵌入式体系和FPGA完结了体系功用。嵌入式微处理器选用Samsung公司的ARM7TDMI系列处理器S3C44B0X;FPGA选用Alrera公司的APEX20K系列EP20K200E,运用S3C44B0X完结了对EP20K200E的装备,取得了杰出作用。本文对其完结办法予以介绍。

1ARM嵌入式处理器S3C4480X简介

S3C44B0X是Samsung公司专为手持设备和一般运用而规划的高性价比和高性能的嵌入式处理器。其杰出特色它的CPU核选用ARM公司的16/32位ARM7TDMIRISC内核,0.25μmCMOS工艺制作,主频最高可达66MHz,存储器寻址空间达256MB。因为其本钱和功耗低,特别合适对本钱灵敏和功用灵敏的运用场合,如PDA、GPS、LCDGame、E-Book等。

2APEX20K系列FPGA装备办法及装备文件

2.1装备办法介绍

Altera公司的APEX20K系列FPGA能够运用以下办法进行配;

①运用专用装备器材,如EPC16、EPC8、EPC2、EPC1、EPC1441;

②被迫串行办法(PS),运用微处理器的串行步接口或ByteBlaster下载电缆;

③被迫并行同步办法(PPS),运用微处理器的并行同步接口;

④被迫并行异步办法(PPA),运用微处理器的并行异步接口;

⑤鸿沟扫描办法(JTAG),运用JTAG下载电缆。

运用办法①时,需求首要运用下载电缆将核算机生成的FPGA装备文件烧入EPC装备器材中,然后由EPC装备器材操控装备时序对FPGA进行装备,一次烧写即可重复运用。运用办法②、③、④时,装备文件事先以二进制办法保存在体系ROM中,能够脱脱离核算机重复运用。若运用方②、③、④时,装备文件事先以二进制办法保存在体系ROM中,能够脱脱离核算机重复运用。若运用办法②,微处理器将装备数据以串行(比特流)办法送给FPGA,在装备时钟驱动下完结装备。若运用办法③,微处理器将装备数据以并行(字节)办法送给FPGA,由FPGA在其内部将并行数据转换成串行数据,该串行化的进程需求外部装备时钟的驱动。在装备时钟速率相同的状况下,办法②、③所用的装备时刻简直相同,但办法②的接口要比办法③简略,若运用办法④,微处理器仍将装备数据以并行办法送给FPGA,在FPGA内部完结数据串行化;与办法③不同的是,该进程不需求外部装备时钟的驱动,但其接口更杂乱,并且需求进行地址译码,增加了体系的杂乱程度,一般很少选用。运用办法⑤时需求核算机的合作,无法在终究的实践体系中脱机运用,此处不予评论。

经过上述评论能够看出,在运用APEX20K系列FPGA开发实践运用体系,特别是要构成某种产品时,假如体系中不含微处理器,只能运用办法①;若体系中含有微处理器,办法①、②、③、④都能够运用,但②、③、④能够发现,办法②的接口最简略,完结起来比其它两种办法都便利因而在含有微处理器的体系中得到了广泛运用,本通讯体系的规划中即选用了该办法。

2.2装备文件的运用

Altera公司的开发工具QuartusII及MAX+PLUSII能够生成多种格局的装备文件,针对不同的装备办法要运用不同格局的装备文件。规划项目编译今后会主动生成.sof文件和.pof文件。其间.pof文件在装备办法①运用专用装备器材时运用,.sof文件用于经过衔接在核算机上的下载电缆直接对FPGA进行装备的场合,装备办法能够是JTAG办法或PS办法中运用ByteBlaster下载电缆的状况。依据.sof文件还能够生成.hex、.rbf和.ttf文件。.hex文件是IntelHex格局的ASCII码文件,第三方的编程器能够运用这种格局的文件对Altera公司的装备器材进行编程。.rbf文件是二进制文件,1字节的rbf数据包括8bit的装备数据,运用时将其存入ROM中。微处理器人ROM运用这种格局的文件。.ttf文件是列表文本文件,.rbf文件的ASCII码存储办法,并且各个字节之间用逗号进行了分隔。假如体系中有其它程序,能够将.ttf文件作为体系程序源代码的一部分,和其它程序一同编译。本体系中选用了.ttf文件作为体系程序的一个头文件运用,其装备数据以数组办法被装备程序运用。关于某种特定类型的FPGA,不管其规划有多杂乱,在相同版别的开发工具下生成的装备文件巨细是相同的。

3被迫串行办法(PS)装备时钟

运用PS办法对FPGA进行装备时,只需求5根信号线,其装备时序如图1所示。

装备时这五根信号线都接至微处理器的I/O上,其间nCONFIG、DCLK、DATA0设置成输出态,由微处理器对FPGA进行操作;nSTATUS/CONF_DONE设置成输入态,由微处理器对FPGA的装备状况进行检测。微处理器首要在nCONFIG信号线上发生一个宽度大于8μs的负脉冲,然后开端检测nSTATUS信号的状况。FPGA检测到nCONFIG信号的下降沿后会迫使nSTATUS和CONF_DONC信号拉低,并且在nCONFIG信号从头举高之间坚持为低电平。NCONFIG信号举高后,nSTATUS将在1μs之内随之举高,微处理器检测到此改变后就以为FPGA现已做好预备能够开端装备。装备第一个上升沿与nSTATUS的上升沿之间要求至少有1μs的时刻距离。因为装备数据是与装备上升沿同步的,在装备时钟的上升沿来之间应当将1bit的装备数据在数据线上预备好,装备数据按低位在先高位在后的次序从数据线上送出。当悉数装备数据送出今后,CONF_DONE信号将被举高,标明装备完毕。微处理器检测到CONF_DONE信号举高,就完毕装备进程。假如装备进程中犯错,FPGA将迫使nSTATUS信号拉低,微处理器检测到此改变将从头开端装备。

装备完毕今后,FPGA还需求个初始化的进程才干进入正常作业状况。在QuartusII或MAX+PLUSII生成的装备文件中现已包括了额定的初始化比特,只需将装备文件数据在装备时钟的同步下悉数送出就现已完结了初始化,用户不用别的加以考虑。

4硬件电路规划

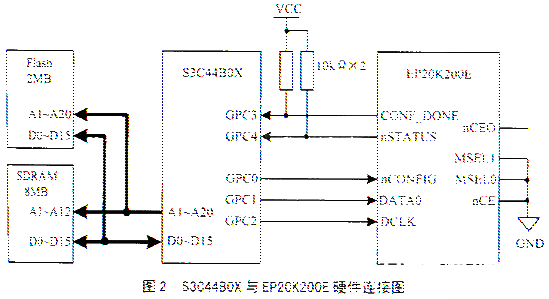

体系的硬件电路规划如图2所示。

因为S3C44B0X内部只要8KB的SRAM作CPU的Cache运用,无法满意体系程序存储及运转的需求,因而需求外挂存储器作为程序保存和运转的空间。体系中运用1片2MB的Flash作为程序存储器,体系的整个运用程序,包括EP20K200E装备程序及装备文件都固化于其间保存。别的运用1片9MB的SDRAM作为体系程序运转空间,S3C44B0X、Flash和SDRAM构成了一个最小的嵌入式体系。Flash、SDRAM与S3C44B0X的衔接办法可参阅S3C44B0X用户手岫。

运用PS装备地需求将EP20K200E的MSEL0、MSEL1、nCE三个引脚接地,然后将EP20K200E的nCONFIG、DATA0、DCLK、CONF_DONE、nSTATUS引脚别离接至S3C44B0X的GPC0、GPC1、GPC2、GPC3、GPC4引脚上。S3C44B0X的I/O口均为多功用口,能够依据运用的需求经过内部寄存器将其设置成输进口、输出口或特别功用口。此处将GPC0、GPC1和GPC2设置成输出口,将GPC3和GPC4设置成输进口。

5软件规划

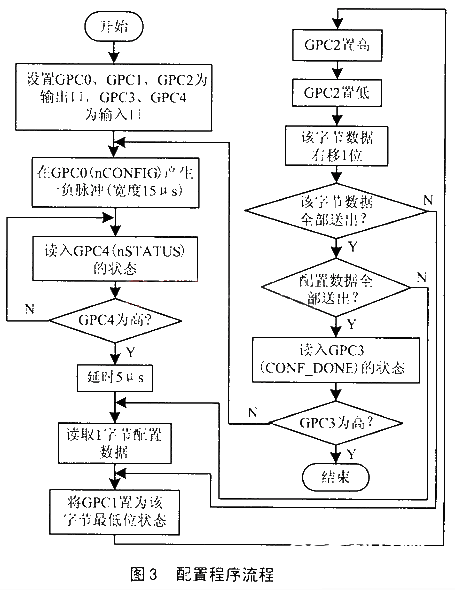

装备时依据装备时序要求,首要在GPC0引脚(对应nCONFIG)发生一个负脉冲,发动装备,然后检测GPC4引脚的nSTATUS信号。NSTATUS信号正常后就在GPC2引脚(对应DCLK)上送装备时钟,在GPC1引脚(对应DATA0)上同步送出装备数据。装备数据以字节为单位从SDRAM中读出,经过移位操作以串行比特流办法从GPC1引脚送出。悉数数据送出后,检测GPC3引脚(对应CONF_DONE)的状况,如为高电平阐明装备成功,不然装备失利,需求从头进行装备。装备程序流程如图3所示。

程序完结运用了C言语。在GPC0引脚发生负脉冲能够经过对其先写0后写1来完结,延时运用简略的循环句子即可,其句子为

rPDATC=rPDATC%26;amp;0xfffe;//*GPC0置低

for(i=0;i《150;i++);//延时15μs

rPDATC=rPDATC|0x0001|;//GPC0置高

其间rPDATC为C端口的数据寄存器。

读入某个引脚的状况并判别其凹凸能够运用一条句子完结,如读入GPC4的状况并判别其凹凸为

while(!rPDATC%26;amp;0x0010));

假如GPC4为低电平,该句子就会一向此处循环,直至其变为高电平。

装备时钟经过在GPC2引脚循环置0、置1来完结,其完结句子为rPDATC=rPDATC|0x0004;//GPC2置高rPDATC=rPDATC%26;amp;0xfffb;//GPC2置低

在GPC2由低变高之前,将1bit的装备数据在GPC1引脚上预备好。

假如装备进程中犯错,EP20K200E将会迫使nSTATUS引脚拉低来告诉S3C44B0X。在本程序中为了主加速装备速度,没有对此进行判别,而是在程序最终经过CONF_DONE信号否举高来判别装备成功与否。假如装备犯错,该信号将不会举高,然后能够从头开端装备。

本国程序、装备文件和体系的其它程序一致编译成一个运用程序存在Flash中,体系加电今后首要运转坐落Flash0地址的引导程序,引导程序完结CPU的初始化,然后将运用程序从Flash复制到SDRAM中,从SDRAM中开端运转。在本体系中运用了实时多使命操作体系(RTOS),在软件规划时将装备程序放在第一个运转的使命中,确保在开机手首要完结FPGA装备。装备所需求的时刻与微处理器的运转速度及装备文件的巨细有关。在本体系中,微处理器运转在64MHz,装备文件的二进制办法有240KB,装备所需的时刻在3s左右。

本文所评论的在嵌入式体系中使用微处理器完结对FPGA装备的计划不只在体系本钱上有优势,并且在体系体积上也有优势,现已在实践体系中得到了运用,取得了杰出作用。本计划虽然是针对APEX20K系列FPGA的,但关于Altera公司其它系列的FPGA产品,只需稍做改动即可加以运用。别的,因为FPGA具有可重复装备的灵敏性,能够在体系中包括多个不同功用的装备文件,运用时依据功用需求进行相应的装备,完结了一机多能。这一点在日益鼓起的软件无线电体系中具有宽广的运用远景。

责任编辑:gt