NVIC: Nested vectored interrupt controller, 嵌套中止向量控制器。

中止与反常:

一切能打断正常履行流的事情都称为反常。 反常与中止的差异在于, 中止请求是来自于Cortex内核外部, 比方各种片上外设, 外部中止请求等, 它们关于内核是”异步”的; 而反常则是因为Cortex内核在履行指令或许拜访存储等操作时所产生的, 关于Cortex内核来说是归于”同步”的(能够拜见Cortex M3威望攻略), 反常和中止一般能够不加区分的运用。

Cortex内核能够支撑多达240个外部中止, 编号16 – 255. 编号1 – 15的为体系反常, 编号0未被运用。

Cortex支行中止嵌套, 答应高优先级的中止抢占低优先级的中止。 Cortex M3/M4可支行多达256级的可编程优先级和128级的抢占, 但有3个体系反常优先级固定, 而且优先级为负数, 高于其它任何反常, 这三个反常分依次为 复位, NMI, Hard Fault.

NMI是Non-Maskable Interrupt(不行屏蔽中止)缩写, 在STM32F4中, NMI被连接到时钟安全体系CCS(Clock security system)反常上。

Hard Fault是总线fault, 存储办理fault, 用法fault所产生的成果, 详细信息能够参阅Cortex M3威望攻略。

优先级存放器

如上所述, Cortex M3/M4支行多达256级的可编程优先级和128级抢占, 每个中止运用一个8位的存放来装备优先级。 但实践一款芯片会依据状况做恰当的精简, 裁剪掉表达优先级的几个低端有用位, 以削减优先级的级数。可是不论运用多少位来表达优先级, 都是以MSB对齐的, 这首要是为了防止程序在不同器材之间移植时不会呈现优先级次序的更改。

抢占优先级和呼应优先级

呼应优先级也叫做 亚优先级 或许 子优先级, 每一个中止都有这两种优先级特点。 当一个低优先级的中止正在履行时, 假如有更高优先级的中止请求, 体系将会呼应这个中止, 即产生中止嵌套。

假如两个中止的优先级相同, 则后来的中止要比及先来的中止履行结束后才会被呼应。 可是假如两个中止一起抵达(或许都在挂起状况), NVIC会依据它们呼应优先级的凹凸来决议呼应那一个。

假如它的的呼应优先级也相同, 那么NVIC会依据它们在中止向量表中的排序先后来决议先呼应那一个。

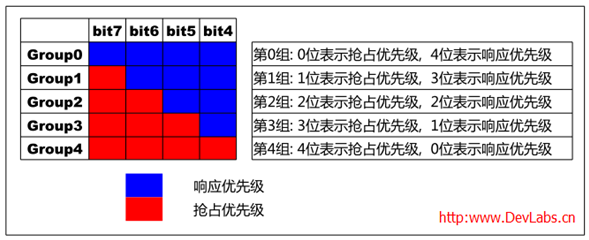

在STM32中运用了4bit来表达抢占优先级和呼应优先级, 有以下5种分组方法:

可见STM32总共供给了16级中止优先级.

来历;21ic