杨志兴,王瑞霞,高长全(电子测验技能要点实验室,山东 青岛 266555)

摘 要:针对PXI测验体系构建中需求的高速数据收集设备,提出一种依据PXI总线的中频数字化仪的规划计划。该设备能够完结400 Msps的实时采样率和14位的采样精度;软件开发形式选用上位机使用程序和底层动态库相结合的开发形式,便利不同用户的定制。驱动程序经过WDM开发,选用Block DMA完结数据的上传。经过联合调试,本体系安稳作业在Windows渠道下,完结了数字化仪要求的各项功用。不只满意当时项目的需求,还可使用于雷达、电子对抗等PXI自动测验体系构建中。

要害词:PXI;中频数字化仪;WDM; Block DMA;中止

0 导言

近年来跟着科技的不断进步,高速数据收集体系不断地向高精度、高速率、小型化等方向开展。尤其在一些特定场合,比方舰船、飞机等环境下,其对测验设备的小型化提出了更高的要求 [1] 。而PXI因为其本身的架构及特色 [2] ,特别合适这种对体积要求严苛的环境中。其间PXI中频数字化仪作为模块化测验体系的重要组成部分,因为其技能难度高、开发规划难度大成为体系集成中的短板,相关产品只能经过国外收购,首要存在如下的问题:收购周期长、本钱贵重、技能不可控,修理困难,严峻限制着PXI模块化体系的自主开展。

本文依据“虚拟仪器”的规划理念并结合近期从事的PXI组成仪器项目需求,提出一种依据PXI总线的中频数字化仪完结计划,即可满意软件无线电体系构建的需求,一起也可作为独自PXI模块进行数据收集、处理和剖析。

1 硬件规划

1.1 整体计划

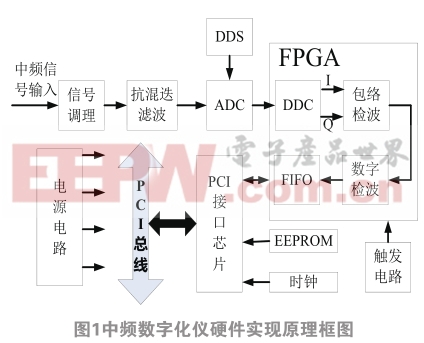

本文研发的中频PXI数字化仪模块是一个单槽3U尺度模块,14位笔直分辨率,最高采样率达400MHzSa/s。其整体硬件框图如图1所示。

首要包含:信号调度部分、抗混叠滤波、DDS部分、A/D转化部分、FPGA操控部分、PCI接口部分和电源等部分组成。其间:信号调度部分完结模仿信号的放大和滤波;ADC部分首要完结信号由模仿到数字信号的转化;FPGA部分首要是完结数字下变频、包络检波以及电路的操控等;PCI总线接口作为数字化仪与PC机的接口,完结数字化仪和上位机软件的信息交互,包含指令下发和数据上传等。

整机作业原理如下:在触发信号到来之后,首要对输入中频信号进行调度,完结模仿中频信号的程控增益操控、抗混叠滤波等,预处理后的中频信号经过高速ADC采样,采样数据送入FPGA进行数字下变频操作变换到基带构成IQ信号,之后依据需求进行复数FFT操作得到频谱数据存储到板载缓存中。此刻FPGA将使本地信号(LINT#)信号有用,引发PCI9054的本地中止,接着会触发PCI中止信号INTA#,向计算机发送中止恳求。主机CPU呼应中止以Block DMA办法读取FIF0中的频谱数据,然后完结一次数据传输。终究在上位机软件中进行处理和显现。

1.2 PXI接口规划

现在首要存在2种计划完结PXI接口电路 [3] :①选用可编程逻辑器件;②选用专用的PCI接口芯片。在本规划中考虑到数字化仪板卡的体积、本钱和开发周期,选用PLX公司的专用的PCI接口芯片PCI9054来完结PXI接口,接口完结示目的如图2所示。

为了习惯不同的部分处理器,PCI9054部分总线类型有3种:C形式,M形式,J形式。本文选用C形式(MODE[1:0]=00),即地址线和数据线分隔形式 [3] 。本规划中发送指令时作业在PCI Target形式,而读取数据的时分则作业在DMA形式。在DMA办法下,数据传输不同于一般的I/O读写办法,它是由PCI9054接收PXI总线,担任完结数据在CPU和硬件设备之间进行数据传输,而无需CPU的干涉。本规划中只触及数据从Local侧到PCI侧的传输,因而挑选DMA0通道并选用block DMA的传输办法完结FIFO缓冲区的频谱数据的读取操作。

2 软件规划

2.1 软件体系结构

完结数字化仪硬件规划之后,就需求开发相应的软件,由软硬件协同合作才干整个数字化仪模块的具体功用。整套中频数字化仪软件体系由上位机使用程序、动态链接库和驱动程序构成,其体系结构如图3所示。

2.2 整机作业流程

数字化仪程序的作业流程如下:首要是数字化仪硬件的初始化,完结后,由上位机软件依据用户选定的功用和输入的参数构成操控指令经过驱动程序将其下发到硬件板卡。PXI板卡进行相应的参数分化构成有用的硬件动作指令完结数据的收集,收集一定量的中频数据后构成硬件中止给驱动程序,上位机呼应中止并经过DMA的办法将数据读取到上位机软件中,然后完结一次有用的数据收集和传输。之后再由上位机软件进行相应的处理、显现和存储等功用。

2.3 驱动程序规划

因为本规划中的PXI中频数字化仪不属于Windows规范的外部设备,因而为了能够运转在Windows渠道上,需求开发相应的驱动程序。Windows操作体系下,开发设备驱动程序的办法有很多种,本文选用DriverStudio东西进行WDM设备驱动程序的开发。

首要,使用DriverStudio中的DriverWorks [5] 生成驱动程序结构,之后需求依据功用要求来增加相应的代码。驱动程序的开发触及到硬件拜访、中止操控和DMA传输等功用模块。限于篇幅,本文要点论述中止和DMA的完结进程。

2.3.1 中止完结

从上文介绍的数字化仪整机运转原理中能够看出,数字化仪的数据收集进程相对于上位机软件的运转,是一种彻底异步的进程。为了完结两者的同步,需求借助于中止来完结。本规划中需求处理的中止类型有2种:①本地中止,即当FIFO中的数据收集半满之后,由FPGA经过LINT#信号发给PCI9054;②DMA中止,当上位机软件收到PCI9054的本地中止后,开端发动DMA读操作。当DMA传输完结后由DMA中止操控器发生。两种中止存在先后联系,只要2个中止的和谐合作才干完结1次中频数据的正确传输使命。

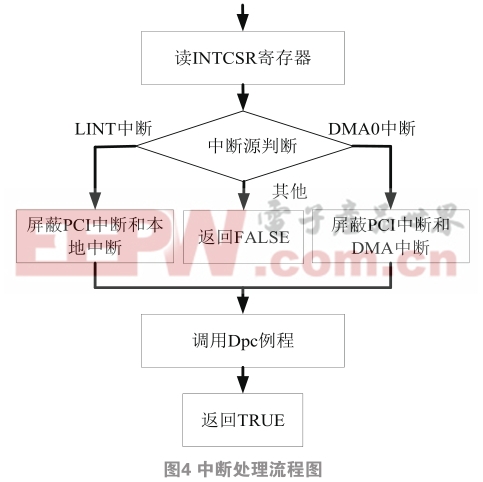

因为这两种中止同享同一个中止服务例程,因而需求在中止服务例程 [6] (ISR,Interrupt Service Routine)中进行中止源辨认,再进行对应处理。本规划中的中止处理流程如图所示。

中止完结部分的要害代码如下:

BOOLEAN Digitizer::Isr_Irq(void)

{

t<<”enter Isr_Irq.”<<EOL;

ULONG status;

status=m_IoPortRange0.ind(INTCSR);

if((status&0x8000)!=0)

{

m_LocInt=1;

t<<”Local Interrup”<<EOL;

m_IoPortRange0.outd(INTCSR,0x40100);

m_IoPortRange0.outd(DMAMODE0,0x20C01);

m_DpcFor_Irq.Request(NULL,NULL);

return TRUE;

}

else if((status&0x200000)!=0)

{

m_LocInt=0;//DMA0

t<<”DMA Interrup”<<EOL;

m_IoPortRange0.outb(DMACSR0,0x8);

m_DpcFor_Irq.Request(NULL,NULL);

return TRUE;

}

else

{

t<<”Interrupt didn’t happen.”<<EOL;

return FALSE;

}

}

2.3.2 DMA完结

为了开发DMA功用,结合硬件规划和软件开发结构,开发人员需求对PCI9054芯片和Driver Studio开发结构均要了解,只要软硬件合作才干完结DMA功用。PCI9054芯片中的DMA硬件支撑部分在其数据手册中具体的介绍,这儿不再叙说。下面要点从软件开发视点进行介绍。

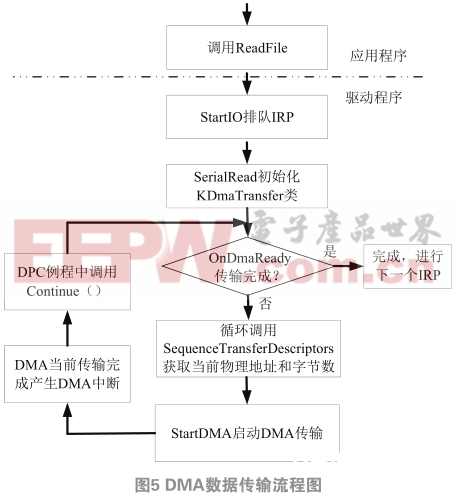

DriverWorks供给了3个类来完结,别离是:KDmaAdapter,KDmaTransfer,KcommonDmaBuffer。其间,KdmaAdapter类用于树立1个DMA适配器,标明1个DMA通道的特性和供给串行化拜访的服务;KDmaTransfer类用于操控DMA的传输,发动1个DMA传输、DMA传输数据缓冲区物理地址和传输字节数以及DMA传输完毕后数据由共用缓冲区拷贝到使用程序数据缓冲区;KcommonDmaBuffer类用于恳求体系供给的共用缓冲区 [8] 。整个DMA数据传输的流程如图5所示。

首要,当使用程序检测到硬件板卡完结1次中频数据收集后,经过调用Win32 API函数ReadFile()函数发动数据的读取 [9] 。由体系的I/O管理器将这个恳求封装成一个相应的恳求包(IRP),然将其传递给驱动程序。驱动程序首要将其进行行列化,构成1个新的串行IRP传递给SerialRead例程 [10] ,在该例程中,经过初始化KDmaTransfer类的实例并在OnDmaReady回调函数发动DMA传输和判别传输是否完结。限于篇幅,本文只给出完结DMA的要害代码:

VOID Digitizer::StartDMA(ULONG PAddress,

ULONG NBytes)

{

t<<”Entering StartDMA”<<EOL;

m_IoPortRange0.outd(DMAMODE0,0x20DC1);

m_IoPortRange0.outd(DMAPADR0,PAddress);

m_IoPortRange0.outd(DMALADR0,0x8);

m_IoPortRange0.outd(DMASIZ0,NBytes);

m_IoPortRange0.outd(DMADPR0,0x8);

m_IoPortRange0.outb(DMACSR0,0x3);

}

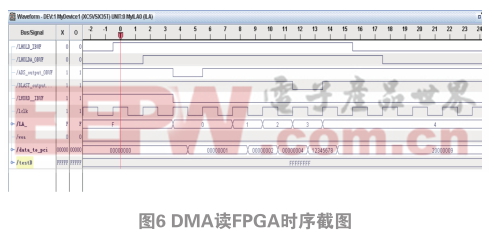

图6是本规划中的DMA读操作在FPGA中的时序图。

2.4 使用程序规划

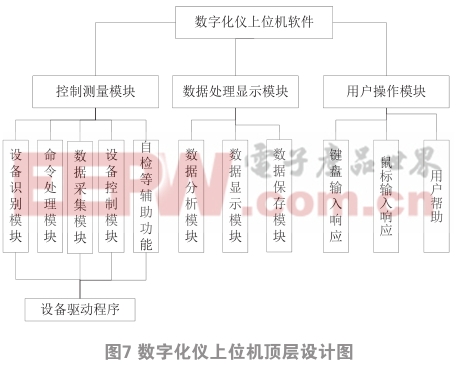

上位机使用软件选用模块化、分层规划的思维,将软件依照功用划分为操控丈量模块、数据剖析模块和用户操作模块,开发言语选用当下较为盛行的C#。体系软件顶层规划图如图7所示。

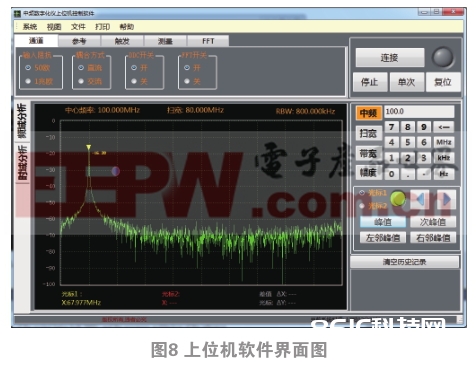

整个软件从功用上能够分为操控丈量模块、数据处理显现模块和用户操作模块。其间操控丈量模块首要完结指令的下传以及收集数据的上报;数据处理显现模块首要是对收集到的信号进行信号处理,包含加窗、FFT、轨道运算、峰值处理、信号录制以及处理结果的显现等;用户操作模块则是供给人机交互的接口,用于将用户的操作指令进行合规性剖析,并将用户的操作目的正确设置到设备中。终究完结的上位机软件效果如图8所示。

3 定论

本文所研讨的中频数字化仪是一种依据PXI总线的模块化中频信号收集仪器,具有高采样率、高分辨率、大数据存储容量以及快速的数据传输等技能,技能完结上彻底自主可控。在软件规划上选用虚拟仪器的规划思维,依照模块化和层次化进行开发,别离完结了上位机软件规划和底层驱动程序开发。现在,本体系能够安稳作业在Windows7渠道下,完结了中频数字化仪要求的各项功用,不光满意了当时的PXI测验体系构建的需求,并且供给了一个较为通用的驱动程序包,能够使用到其他需求中频数字化仪的PXI测验体系中。

参考文献:

[1] 郭文飞.依据PXI总线的直升机电气体系测验渠道的研发[D].哈尔滨:哈尔滨工业大学,2016.

[2] 苗忠海.依据PXI总线的数据收集体系规划[J].电子规划工程,2018(12):67-69.

[3] PLX Technology.PCI9054 DataBook.1.0ed.PLX Press,1998:174-298.

[4] 程月平.PCI总线数据收集体系的软件规划[J].外表技能,2017(10):14-17.

[5] 史云辉.依据PCI总线的数据收集卡接口的规划及完结[J].电子测验,2017(10):21-23.

[6] 王海霞.依据PCI总线的四通道CAN通讯卡的规划[J].电子规划工程,2016(5):41-44.

[7] 崔荃.多通道数据收集体系的规划与完结[D].成都:成都理工大学,2015.

[8] 杨亚军.Windows下视频收集卡的WDM驱动开发[D].西安:西安电子科技大学,2015.

[9] 武安河,周利莉.Windows设备驱动程序开发实务[M].北京:电子工业出版社,2001.

[10] 李小平.依据PXI总线结构的数据收集体系规划[D].哈尔滨:哈尔滨工程大学,2017.

(注:本文来源于科技期刊《电子产品世界》2020年第05期第63页,欢迎您写论文时引证,并注明出处。)